Aceasta depinde de tehnologia

Deci, primele lucruri mai întâi.

În cazul siguranțe sau PROM de programare sau „arde“ este de a elimina prin topirea pod durata impulsului de curent fuzibil și de mare amplitudine. Prin urmare, siguranța dispozitivului menționat ca un singur programabile. Jumperii sunt din metal (nicrom, titan-tungsten) sau policristalin (polisiliciu).

În cazul circuitului EPROM programabil electric cu o programare specială și șterse prin iradiere suprafața cristalului la raze ultraviolete puternice (de exemplu, de la o lampă cu mercur) prin fereastra de cuarț în carcasă.

SRAM sau în memoria RAM de acces rus statică aleatoare este caracterizată printr-un consum redus de energie, prin urmare, își găsește aplicarea sa în FPGA. Acest tip de celule de memorie este format din 6-8 tranzistori, deci o densitate scăzută de înregistrare și costul ridicat al kilobytes de stocare a informatiei. În general, totul este destul de simplu și obișnuit.

Dar antifuse - este cel mai interesant. Că au construit FPGA foarte Rad-tare (RTAX si RTSX-SU) societate Actel, care a adus-o atât de faimos. Ca și în cazul siguranței ei o dată-fuzibil (deși nu întotdeauna, ci mai mult pe aceasta mai jos). Cu toate acestea, design-ul este o diferență fundamentală - au format un dielectric cu trei straturi de oxid-nitrid-oxid (ONO) și este chiar opusul.

Inițial, internetul are o astfel de rezistență ridicată, ajungând la mai multe milioane de ohmi. Atunci când se aplică tensiunea între stratul de difuzie și anvelopa de siliciu (în figură - poarta) duce la apariția în efectul de oxid de tunelare Fowler-Nordheim efect tunel și direct. Acest lucru duce la o creștere a curenților de scurgere și defalcare moale (defalcare reversibilă). În cazul în care câmpul electric este îndepărtat, rezistența dielectrică de restaurare. Altfel curenții vor crește, iar acest lucru va duce la termic (ireversibil) al descompunerii dielectrice, formarea unui canal conductor și o creștere bruscă a curentului prin acesta. Acest script este în literatura occidentală ca defalcare greu.

parametrii de stat jumperului după pauză ar trebui să fie menținută timp de aproximativ 40 de ani. rezistență scăzută și parazitare scăzută tipuri de antifuse pe bună dreptate-au link-uri de STI un efect pozitiv asupra semnalelor neniya rata de prevalență în conexiuni programabile.

Sub programare Masca se înțelege aplicarea stratului de metalizare superior cristal 1-2 semifinisate urmată de gravură.

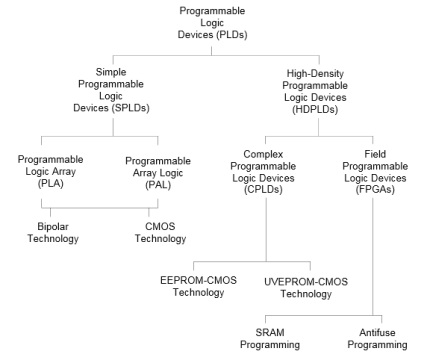

Să mergem mai departe după introducerea de lungă durată, de fapt, la subiectul indicat în titlu. PLD dispozitive în funcție de numărul de porți, arhitectura și caracteristicile tehnologiei de programare poate atribuite claselor reprezentate în schema de mai jos

Gate matrice (FPGA)

În terminologia adoptată în Occident, de asemenea, cunoscut sub numele de HAL (Hard Array Logic) sau Structured ASIC. Ceva între un circuit integrat specific și PLD. Cu mai întâi în comun este că programarea se face punct de vedere tehnologic. Cu al doilea este faptul că pe un singur cip poate obține o varietate de dispozitive digitale.

Programarea se realizează prin aplicarea 1-2, urmată de gravare a straturilor de metalizare pe cristal semifinit cu celule neskommutirovannymi. Construit folosind dezvoltatorii de hardware FPGA au posibilitatea de a înlocui FPGA LSI pe bază, în timp ce primește, în unele cazuri, un efect economic semnificativ și creșterea densității aparatului de aspect. Pentru a asigura o astfel de producători de prelucrare sunt în curs de dezvoltare de software CAD permite proiecte de traducere automată efectuate pe baza bibliotecilor FPGA FPGA.

Poate cuprinde până la 100.000 de porți și funcționează la frecvențe de până la 50MHz. Ciclul de funcționare este de aproximativ 3 luni.

În prezent, aproape în întregime de suplinit FPGA și CPLD. Cu toate acestea, se aplică producției la scară mică, având în vedere costurile scăzute în raport cu chips-uri înregistrate. interne disponibile de Angstrom. ONG-urile Fizică și alte câteva întreprinderi.

Programmable Array Logic (PAL)

Se compune din logica de intrare-ieșire și miezul, care este un bine-cunoscut pentru noi toți EPROM sau EEPROM. Folosit pentru a crea circuite logichekih kobinatsionnyh. Pentru prorgammrovaniya PAL suschestovali limbaje de programare speciale, cum ar fi PALASM, ABEL, CUPL. PAL timpurie produs prin tehnologie bipolară, cu o singură programare prin epuizare titan-tungsten straturi subțiri (siguranțe). Mai târziu - în tehnologie CMOS. Ele constau din zeci la sute de supape.

Ca BMC acum înlocuite cu dispozitive mai sofisticate, dar este încă folosit în produse pentru scopuri speciale, cum ar fi echipamentele militare. Produs de Atmel

Programabil logic array (PLA)

Acesta diferă de clasa anterioară, care sunt programate într-o matrice sau, și AND. Din acest motiv - și costurile sistemelor de mai complexe este mai mare decât cea a PAL. Datorită faptului că ambele matrice sunt programabile, viteza este mai mică decât în cazul PAL.

Complex Dispozitiv Logic programabil (CPLD)

Tehnologia de dispozitive logice programabile la complexitatea, care ocupă intervalul între aproximativ PAL (Programmable Array Logic) și FPGA (Câmp-gate array programabile), și cu o combinație de caracteristici arhitecturale.

Dispozitiv CPLD includ mii - zeci de mii de celule sunt bine întârziere de propagare previzibile. Din FPGA distinge prin prezența memoriei reprogramabilă non-volatilă, cele pentru încărcarea inițială a configurației nu are nevoie de un cip de memorie, la fel ca în cazul FPGA. Prin urmare, resursa reprogramare este mai mică decât în cazul celor din urmă (nu mai puțin de 1 000 de cicluri de înregistrare / ștergere pentru familia Xilinx CoolRunner-II).

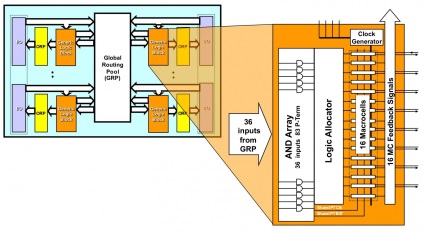

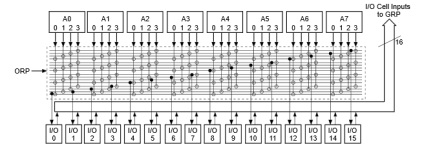

CPLD Structura este un set de blocuri funcționale de matrice unite de comutare globală de rutare Pool. Arhitectura blocurilor funcționale (Generic Array Logic) în mai multe moduri este similar cu arhitectura PAL universale. Diferențele constau în faptul că toate Macrocell de ieșire (Macrocells) au două feedback-uri, și macrocelule autobuz intermediare sunt atribuite prin intermediul unui distribuitor (repartitor Logic). Unele CPLD macrocelule nu au nici o conexiune la ieșire externă. Astfel de macrocelule numit ascunse. macrocelule ascunse au doar un singur feedback-ul.

ieșiri externe CPLD se leagă la macrocell ieșire folosind un alt ORP mezhsodineny matrice (ieșire Routing Pool). Aceeași matrice conectează logica de intrare la GRP. Pentru a reduce întârzierile în unele CPLD furnizează intrări de intrare directe conectate direct la intrările de macrocelule.

Câmp-Gate Array programabile (FPGA)

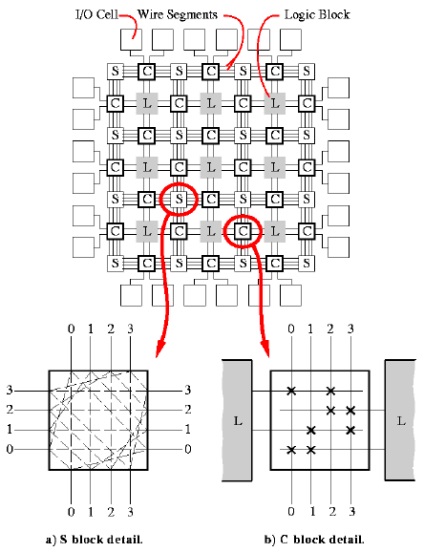

În ciuda diferențelor dintre diferitele familii FPGA și de la diferiți producători, care sunt incluse în compoziția lor bunătăți, cum ar fi DSP și unități de bază procesor, principiile generale ale arhitecturii FPGA rămân neschimbate.

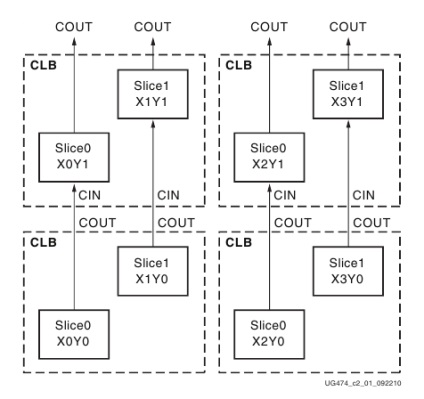

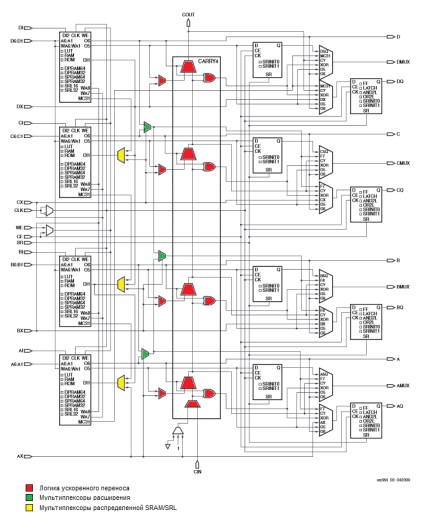

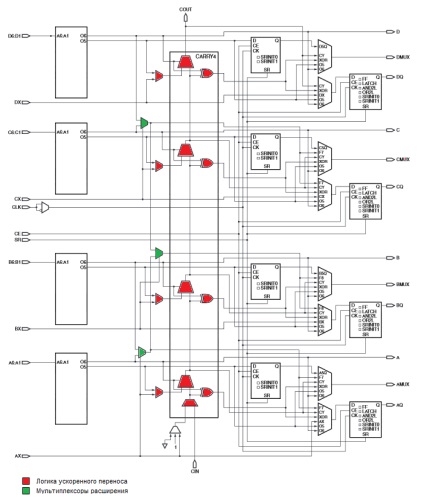

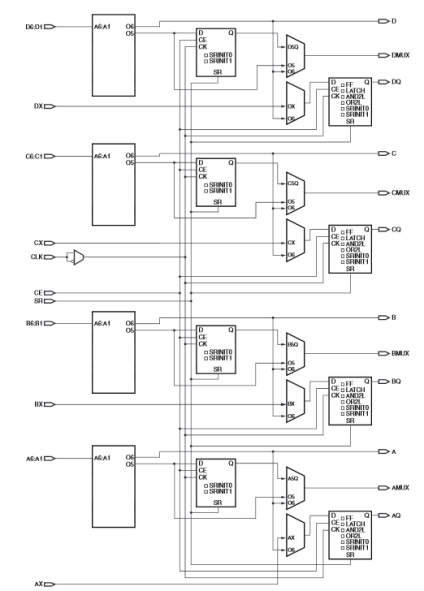

Principala unitate funcțională a FPGA este CLB (Configurable Logic Block). CLB comutare realizată de S (caseta de conectare) bloc și blocuri C. CLB, la rândul lor, pot include mai multe LUT (tabelul Look-up). Firma Xilinx CLB, de asemenea, consta dintr-un așa-numite slice, care, de asemenea, la rândul lor, sunt compuse din LUTov. Deci, de ce complica lucrurile? Faptul că există diferite tipuri de secțiuni Slice, Luty care au caracteristici diferite.

Familiile FPGA Virtex-6 și Spartan-6 CLB este format din 2 secțiuni de 3 tipuri: SLICEM, SLICEL și SLICEX. Familia Spartan-6 un CLB cuprinde SLICEL și SCLCEX, iar celălalt dintre SLICEL și SLICEM. În Virtex-6, arată un pic diferit - unul este în secțiunea 2 SLICEL, iar secunda - si SLICEL SLICEM. În fiecare secțiune un CLB conectat la un transfer de lanț separat.

Să luăm în considerare fiecare dintre aceste secțiuni.

SLICEM cuprinde 4 LUT, include logica transportului accelerate, tabelul de conversie, care poate fi configurat ca o memorie distribuită și SRL (Shift tabel registru de căutare) și multiplexoare extinde numărul de argumente booleene

SLICEL cuprinde 4 LUT, include logica accelerată de transport și multiplexoare extinde numărul de argumente booleene

SLICEX este format din 4 UTT, numai logica. Nu memorie partajată, circuitele de transfer și multiplexoare expansiune.

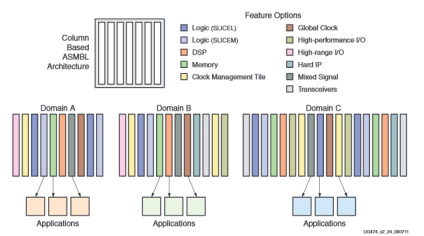

Cum toate aceste conecta împreună? În acest scop, compania a dezvoltat o arhitectură Xilinx ASMBL (Application Specific Modular Block Architecture). Pe scurt, blocuri identice, cum ar fi un DSP, IP-blocuri bloc de memorie încorporate sau secțiuni logice sunt aranjate într-un singur rând. Prin combinarea acestor serii și obținute FPGA specializate pentru diferite aplicații (de exemplu, Virtex-6 sunt LXT, SXT și HXT).

IO unități FPGA moderne este menținută peste 40 de protocoale diferite, cu tensiuni diferite, cum ar fi: LVCMOS, LVDS, Bus LVDS, LVPECL, SSTL, HSTL, RSDS_25 (point-to-point), PCI, I2C și altele. Concluzii FPGA împreună în băncile 30-80 terminale fiecare, fiecare terminale bancare pot sprijini diferite grupuri de standarde.

- Soloviev, A. Klimovich, Introducere în proiectarea de circuite combinaționale în FPGA.

- Daniel Gomez-Prado, Maciej Ciselsky, un tutorial pe FPGA de rutare.