Rezumat: Prelegerea introduce o compilație și o reprezentare interpretativă a schemei logice. Gestionarea procesului de modelare este considerată, sunt descriși principalele algoritmi de simulare a evenimentelor schemelor logice.

Modele de circuite interne (mașini)

După introducerea descrierii externe a telecomenzii în computer. se traduce în reprezentarea internă a dispozitivului, care este utilizată direct în procesul de modelare logică. Există două forme principale (modele) ale reprezentării interne a DU - compilativă și interpretativă. Când compilatory descrierea modelului controler extern ca un model structural (schemă) sau folosind funcțional program de difuzare YARP în unele limbaj de programare (de obicei, C sau limbaj de asamblare), care realizează în mod direct procesul de modelare. În modelul interpretativ, descrierea externă este tradusă într-un sistem de tabele legate, care sunt apoi utilizate de programul universal de modelare.

Modelul de compilare

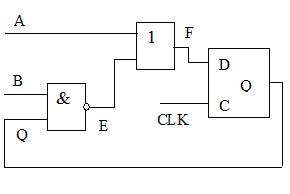

În metoda de modelare a compilării, descrierea schemă este tradusă într-o secvență de instrucțiuni ale limbajului de programare sau ale instrucțiunilor mașinii. De exemplu, diagrama de secvențe sincrone prezentată în Figura 5.1 poate fi tradusă în următorul program, prezentat mai jos în lista "Modelul de compilare".

Algoritmul de modelare a compilației [39] este prezentat ca un pseudocod în lista "Modelare compilație". Trebuie să acordați atenție faptului că este necesar să acordați prioritate schemei după niveluri. Principalul avantaj al metodei de compilare a modelării este viteza mare. Dezavantajele sunt că modelul trebuie re-compilat de fiecare dată când schimbați schema (în procesul de proiectare). Aici, de regulă, folosim modelarea de la capăt la capăt (nu pe bază de eveniment), în care la fiecare iterație se recalculează valoarea fiecărui element logic.

Fig. 5.1. Schema pentru modelul de compilare

În plus, este necesară pre-ruperea feedback-ului pentru circuitele secvențiale (pentru aceasta au fost dezvoltate algoritmii corespunzători). Dar problema principală a acestei metode este luarea în considerare a întârzierilor în timp ale elementelor logice. Prin urmare, această metodă este folosită în principal în modelarea circuitelor secvențiale combinaționale și sincrone. În acest caz, de regulă, numai logica este verificată, nu relațiile de timp.

Model interpretare