Au fost formate 3 contururi. Două contururi de două elemente și un contur de patru elemente.

Pentru a scrie formula structurală în baza lui N-N, vom folosi legea dublei negări () și a legii lui de Morgan ().

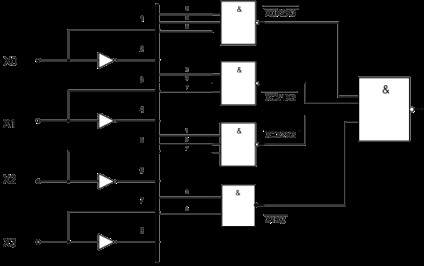

Schema structurală a CS în baza NAND este prezentată în figura 1.

Figura 1. Schema structurală a CS în baza NAND

Multi-bit adder cu transport accelerat.

Un adder este un dispozitiv logic combinat conceput pentru a efectua o adăugare aritmetică de numere în cod binar.

Schema de transfer accelerată este o schemă logică pentru calculul semnalului de transfer accelerat. Aplicabil în cazul unei creșteri accelerată.

De obicei, schemele de transfer accelerat se fac pentru un grup de 4 cifre. Calcul timp semnale de transfer C1, C2, C3 și C4 ale semnalelor de intrare este același, și 3 * dt (1 * dt - calcularea semnalelor pi și Gi + 2 * dt - calcularea semnalelor de transfer). În acest caz, timpul de adăugare într-un grup de 4 cifre este egal cu:

t4 = tc + ts = 3 * dt + 2 * dt = 5 * dt, unde

tc este timpul de calcul al semnalului de transmisie,

ts este timpul necesar pentru calcularea modulului semnalului sum.

În totalizatorii cu o capacitate mai mare de biți, grupurile pe 4 biți sunt conectate secvențial și se adaugă scheme suplimentare pentru transportul accelerat al celui de-al doilea și al treilea nivel.

1. la adderul de 64 biți cu schemele de transfer accelerat al primului nivel, timpul de adăugare este:

t64 = 16 * t4 = 16 * 5 * dt = 90 * dt, accelerarea adăugării în 191/90 = 2,12 ori.

2. la adderul de 64 de biți cu schemele de transfer accelerat al primului și al doilea nivel, timpul de adăugare este:

t64 = 3 * dt + 3 * dt * 4 + 3 * dt = 18 * dt, accelerarea adăugării în 191/15 = 10,61 ori.

3. În cazul adder-ului pe 64 de biți cu schemele de transfer accelerat ale primului, al doilea și al treilea nivel, timpul de adăugare este:

t64 = 3 * dt + 3 * dt + 3 * dt + 3 * dt = 12 * dt, accelerarea adăugării în 191/12 = 15,91 ori.

Conform tabelului de comutare, în cazul general, pentru semnalul de transfer al oricărui bit i, se aplică următoarea relație:

Tabelul 3. Tabela de comutare

Valorile gi, ri sunt calculate ca rezultate intermediare și în suma totală. Semnificația acestor cantități poate fi explicată foarte simplu. Semnalul gi este generat atunci când, într-o descărcare dată, transferul are loc datorită unei combinații a variabilelor de intrare ai, bi. Prin urmare, se numește funcția de generare a transferului. Semnalul Pi indică dacă semnalul de transmisie Ci recepționat în cifra cea mai puțin semnificativă este transmis în continuare. Prin urmare, se numește funcția de propagare a transferului.

Folosind expresia (1), putem deduce următoarele formule pentru calculul semnalelor de transport:

Evident, deși expresiile obținute sunt destul de complexe, timpul pentru generarea unui semnal de transmis la orice bit cu ajutorul funcțiilor auxiliare este determinat numai de timpul de întârziere a propagării semnalului pe cele două elemente. Aceste funcții sunt realizate printr-un dispozitiv special de combinare - schema de transfer accelerat.

În Fig. 2 prezintă o diagramă a unui dispozitiv de transfer paralel într-un grup de patru cifre. Această schemă realizează sistemul de ecuații (2).

Figura 2 Schema de transfer accelerat

Circuitul este fabricat într-o versiune integrată.

Adăugarea de numere care conțin mai mult de patru cifre poate fi realizată prin conectarea mai multor ediții de patru margini.

Schema și principiul funcționării

Figura 3. ADC paralel

Semnalul de intrare este alimentat la intrările inversoare ale comparatoarelor (DA1-DA8) conectate în paralel. Pe non-inversoare intrări ale acestor comparatoare sunt alimentate cu tensiunea de referință la rezistoare divizor de tensiune R1-R9, la fiecare comparator este alimentat suport dressing, caracterizat prin învecinându pasul de cuantizare. Numărul de comparatori inclus este convertit în cod binar utilizând codorul prioritar DD1

· Viteză mare, atingând zeci de nanosecunde.

· Complexitate mare (numărul de comparatori din circuit este egal cu numărul de niveluri de cuantificare și este egal cu 2n unde n este adâncimea de biți a codului de ieșire

· Cost ridicat - datorită costurilor ridicate;

· Și, ca o consecință, precizie scăzută (8-10 biți)