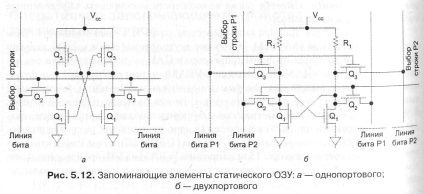

GE dublu port de RAM (vezi. Figura 5.12, b) conține, de asemenea, șase tranzistori, dar spre deosebire de standardul GE (vezi. Figura 5.12, a) Q3 tranzistori nu servesc ca o rezistență, o asigură accesul la elementul din două direcții.

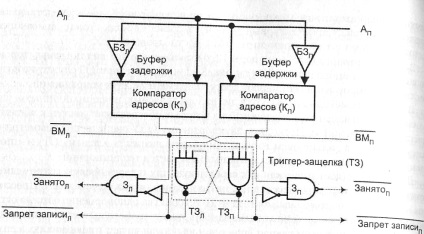

Fig. 5.14. Logica arbitrajului în chip este implementată în hardware.

Fig. 5.14. Logica arbitrajului folosind semnalul "Ocupat"

Dacă apelurile către aceeași celulă apar strict în același timp, semnalele de la ieșirile Kl și Kp vor merge simultan la intrările TK. Schema TK este implementată astfel încât declanșatorul să se stabilească în acest caz și în una din cele două stări normale, ceea ce garantează o decizie pozitivă de accesare a celulei în favoarea unuia dintre porturi.

Semnalele pentru selectarea cipului VLM și VM provin direct de la TK, datorită căruia, dacă există un apel de la un singur port, arbitrajul nu este efectuat.

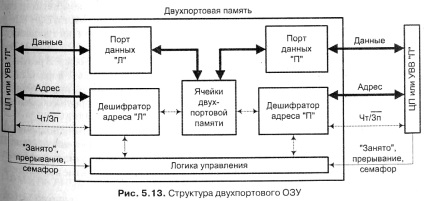

În plus față de abilitatea de a accesa celulele din două direcții, memoria cu două porturi este echipată cu mijloace de schimb de mesaje între dispozitivele conectate la acesta: un sistem de întrerupere și un sistem semafor. Primul dintre ele se numește unul hardware, iar cel de-al doilea se numește unul software.

Adesea, un cip de memorie multiport nu este suficient din cauza lipsei de capacitate a unui IMS sau din cauza numărului mic de celule. În ambele cazuri este necesar să conectați mai multe jetoane, respectiv, în paralel sau în serie. Dacă mai multe cipuri sunt combinate într-un lanț pentru a obține lățimea dorită a cuvântului, apare o problemă cu arbitrajul atunci când accesați simultan aceeași celulă. În aceste cazuri, în diferite IC-uri ale lanțului, datorită răspândirii parametrilor lor, preferința poate fi dată porturilor diferite, în timp ce soluția trebuie să fie unificată. Pentru a elimina această situație, chipsurile de memorie multiport sunt disponibile în două versiuni: master și slave. Decizia se face numai în microcircuitele de conducere, iar sclavii operează în conformitate cu instrucțiunile primite de la comandant. Astfel, în lanț se folosește doar un chip de tip "master", iar toate celelalte IC-uri ar trebui să fie de tip "sclav".