Pentru a mări adâncimea de biți, CPU este alcătuit din mai multe secțiuni.

În ciuda faptului că în momentul de față se termină lansarea procesoarelor partiționate, examinarea lor va oferi o înțelegere mai profundă a principiilor construirii și funcționării microprocesoarelor moderne cu un singur chip și a sistemelor bazate pe acestea. Mai mult, este luat în considerare microprocesorul K584 partiționat.

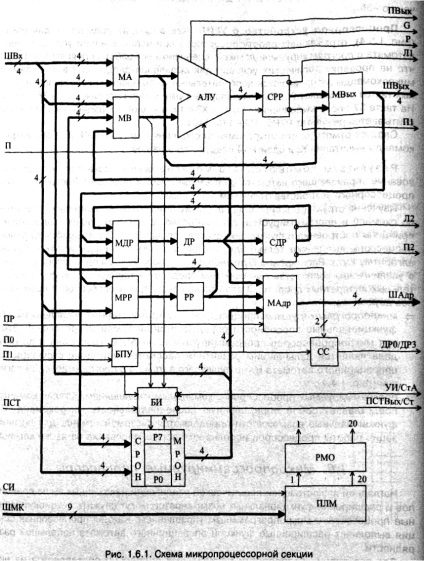

Structura organizatorică funcțională a procesorului. Schema bloc a unei secțiuni microprocesor separate este prezentată în Fig. 1.6.1.

Secțiunea cuprinde următoarele noduri:

● Unitatea logică aritmetică (ALU). Acesta este conceput pentru a efectua opt operații aritmetice și opt logice. Intrările ALU sunt operanții A, B și semnalul AL al transferului ALU. Din ieșirile ALU, rezultatele operațiilor pe operanții A, B, precum și semnalul de ieșire al transferului PV al ALU și semnalele G, P pentru transferul accelerat sunt eliminate;

● Registrul de funcționare (PP). îndeplinirea funcțiilor de bază în procesarea informațiilor;

● registru suplimentar (DR). sau registrul extensiei de lucru utilizate în operațiuni de precizie dublă,

● bloc bloc de scop general (POH). constând din opt registre P0. P7, destinat stocării și schimbului de informații între blocuri de secțiuni. Înregistrarea P7 este de obicei folosită pentru a efectua funcțiile contorului care oferă secvența de comandă: atunci când conținutul contorului este incrementat cu +1, se execută următoarea microinstrucție; cu o creștere de +2, următoarea microcomandă este omisă; modul fără cont este folosit pentru a introduce conținut nou în P7, care este necesar pentru implementarea tranzițiilor;

● Unitate de control poziționare (PSU). efectuând modificările necesare în activitatea secțiunii, în funcție de poziția pe care o ocupă (junior, mediu, senior) în procesor, alcătuită din mai multe secțiuni. Poziția necesară a secțiunii este stabilită prin intermediul semnalelor P1, P0;

● Schimbătoarele de registru pentru lucrători și auxiliari (CPR, SDR) atunci când folosesc semnalele BPU permit efectuarea operațiilor de schimbare a conținutului registrelor specificate;

● schema de selecție (CC), care selectează biții registrului DR suplimentar în funcție de poziția ocupată de secțiune. Cu linia de ieșire cu două funcții, se iau biții inferiori (DRO) sau vârstnici (DRZ) ai conținutului DR;

● Bloc incrementator (BI) pentru modificarea conținutului programului contra contorului în funcție de valorile de transfer contra intrare de semnal (FCS) și controlul incrementator (M) au primit la intrarea lor. Din ieșirea BI bloc eliminat incrementator semnal de ieșire contor transporta (PSTVyh) și cifre mai ridicate de operanzi A (CTA) și B (CTB). selectarea modurilor CC circuit și BI bloc incrementator semnalele coordonate P1, P0 fiind recepționate de către unitatea de intrare de control al poziției BPU (Tabel. 1.6.1). Cu semnalele de pe BI modul de intrare registru set P7 - contor sau POH (tabelul 1.6.2.);

● Un multiplexor (MA) controlează trecerea operatorilor A de la POH sau de la magistrala de intrare (WBX) la intrarea ALU sau a magistralei de ieșire (W). Busurile de intrare și ieșire sunt alcătuite din 4 linii;

● multiplexorul B (MB) controlează trecerea operatorilor B cu PP, DR sau ШВх la intrarea ALU; multiplexorul de ieșire (MVYh) transferă operandul A, precum și operanzii de la ieșirea ALU la ShVyh sau intrările PP, DR, POH;

● o matrice logică programabilă (PLA) convertește codul microinstrucțiunii de 9 biți, care intră în secțiunea de autobuz microinstrucțiunii (MCS), compus din 9-line, 20-bit de control intern cuvânt, oferind controlul funcționării tuturor unităților din secțiunea microprocesor;

● Inregistrare microoperations (RMS) compus din 20- și D -triggerov, pentru stocarea cuvânt de control intern la timpul de execuție microinstrucțiunii. Utilizarea micro registru RMO care este produs de încărcare la marginea ceasului pozitiv (semnalul se schimbă de la 0 la 1), permite în timpul microinstrucțiunii curent pentru a produce PLA recepționează și convertește următorul cod microinstrucțiunii.

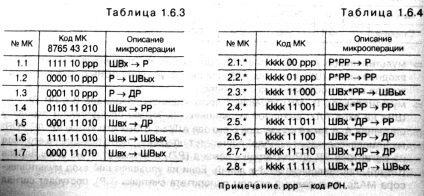

Sistem de microinstrucții. Codul de microcomandă este format din nouă cifre (K8 ÷ K0). Există două formate de coduri microcomandă:

● Primul format conține domeniul operațional al celor mai înalte cifre K8 ÷ K5, care definește în principal funcțiile ALU; un câmp suplimentar din categoriile K4 și K3. Extinderea capacităților de codare; un câmp selector de trei biți inferiori K2 ÷ K0 (ppp), care permite alegerea unuia dintre cele opt POH care participă la operația de micro-operare;

● Al doilea format constă dintr-un câmp care conține toți biții K8 ÷ K0 ai codului MK.

Pentru confortul utilizării, sistemul de microcomenzi este împărțit în șase grupuri. Să luăm în considerare trăsăturile MC ale fiecărui grup.

Grupul 1. Cu ajutorul MC al acestui grup (Tabelul 1.6.3), transferurile MO sunt efectuate între nodurile interne ale UIP fără participarea UAU. Sursa de informații este POH (P) sau ШВх, receptorul este POH (Р), РР, ДР sau ШВых.

Grupul 2. Acest grup (Tabelul 1.6.4) include operații aritmetice și logice efectuate de UAU. Operațiunile indicate în tabelul. 1.6.4 cu un asterisc (*), depind de codul kkkk și sunt date în Tabelul. 1.6.5. Aceste operații se efectuează în general pe operanzii A, B, care intră în ALU prin multiplexoarele A, B (vezi Figura 1.6.1), din sursele indicate în coloana "Descriere a microoperațiilor". 1.6.4 (coloana din stânga se referă la operandul A și la coloana din dreapta la operandul B).

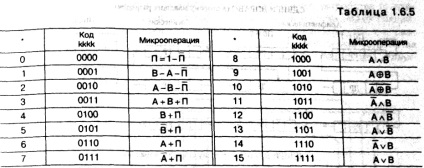

Ar trebui să se distingă trei tipuri de operațiuni (tabelul 1.6.5).

Operații pe doi operanzi. Acestea includ trei (1-3) aritmetice și toate cele opt (8-15) operații logice.

Operații pe un operand. Aceste operațiuni (4-7) vă permit să trimiteți prin operatorii de coduri directe, inversați sau suplimentari ALU și B, precum și transferul în incremente: A + 1, B + 1.

Operațiuni fără participarea operatorilor. Operația P = 1 - ¯P poate fi folosită pentru a seta zerouri și una în toate biții din oricare dintre cele patru receptoare de informație: P, PP, DR, BW.

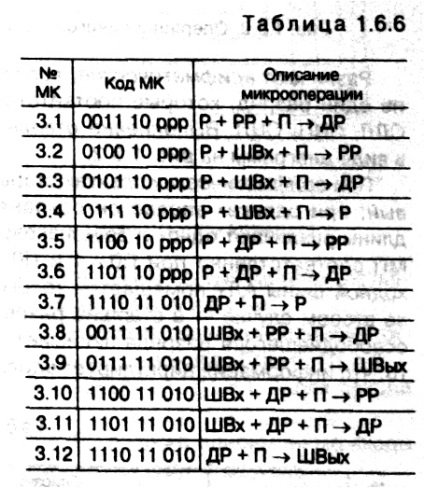

Grupul 3. Operațiunile acestui grup (Tabelul 1.6.6) vă permit să efectuați adăugarea prin combinarea surselor (P, PP DR, BWX) și receptoarelor (P, PP, DW, BW) de informații. Operațiunile DR + P (3.7, 3.12) sunt de fapt operații înainte și complementare ale grupului 1 și este posibil să crească conținutul registrului suplimentar DR.

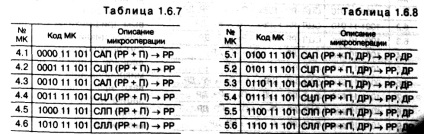

Grupuri 4 și 5. Aceste operații (Tabel. 1.6.7 și 1.6.8), se poate realiza un set complet de schimburi de conținut registru (RR) sau registru dublu-lungime de lucru (RR, DR) compuse dintr-o conexiune serie de PP și DR. În acest ultim caz, este posibil semnal de transfer RR podsummirovaniem P shift aliniere.

Există schimbări aritmetice, logice și ciclice la dreapta și la stânga pentru o singură cifră, care au respectiv desemnările: SAP, SAL, SLP, SDL, SPC, SCL. Execuția operațiilor de schimbare individuală este ilustrată sub forma diagramei din Fig. 1.6.2.

În cazul schimbărilor aritmetice, cifra înaltă (stânga) este utilizată ca semn unic; Când este mutat spre dreapta, rămâne. Atunci când se lucrează cu un dublu operanzi lungime distincția între schimburi mono și două caractere sunt puse în aplicare în poziția ridicată, respectiv MP la P0 și P0 = 1 = 0. În primul caz, cel mai semnificativ bit de autobuz de ieșire ALU este plasat numai în MSB de registru de lucru RR, în al doilea caz - în bitii de înaltă calitate pentru PP și DR. Cu schimbări logice, locul descărcării devine zero. Pentru schimburi ciclice caracteristice că informațiile circulă de-a lungul fără a părăsi registrele lor.

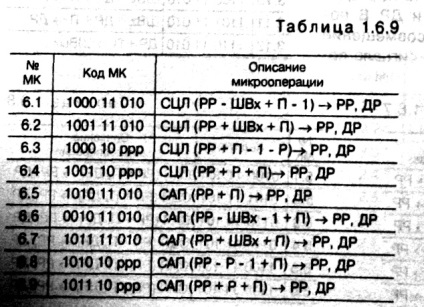

Grupa 6. Operațiunile acestui grup (Tabelul. 1.6.9) permite efectuarea adunare sau scădere, cu semnalul de transfer activ P, cuplat la dreapta sau o aritmetică la stânga rezultat schimbare ciclica registru RR lungime dublă DR Aceste micro-operații asigură punerea în aplicare eficientă a înmulțire și împărțire algoritmi binare numere.

Recomanda acest articol altora!