FPGA este o abreviere pentru fraza engleza Field Programmable Gate Array.

FPGA este o abreviere pentru fraza "Schemă Integrală Logică Programabilă". Cuvântul FPGA se găsește în documentația și descrierile în limba rusă în loc de cuvântul FPGA. Mai departe, în text, acest termen va fi utilizat - FPGA.

FPGA și FPGA sunt abrevieri pentru aceeași clasă de componente electronice, microcircuite. Acestea sunt microcircuitele folosite pentru a crea structura intrinsecă a circuitelor digitale integrate.

Logica FPGA nu este determinată de producătorul chip-ului, ci de programarea suplimentară (în câmp, programabilă pe câmp) cu ajutorul unor instrumente speciale: programatori și software.

Cipurile FPGA nu sunt microprocesoare, în care programul de utilizator este executat secvențial, echipa de la comandă. În FPGA se realizează exact un circuit electronic, constând din logică și declanșatoare.

Proiectul pentru FPGA poate fi dezvoltat, de exemplu, sub forma unei scheme de circuit. Există, de asemenea, limbi speciale pentru descrierea hardware-ului, cum ar fi Verilog sau VHDL.

În orice caz, descrierea grafică și text a proiectului implementează o schemă electronică digitală, care va fi în cele din urmă "încorporată" în FPGA.

De obicei, chip-ul FPGA în sine constă în:

- blocuri logice configurabile care implementează funcția logică necesară;

- comunicații electronice programabile între blocurile logice configurabile;

- plăci de intrare / ieșire programabile, care asigură conectarea ieșirii externe a chip-ului cu logică internă.

În mod strict vorbind, aceasta nu este o listă completă. În FPGA-uri moderne, blocuri de memorie, blocuri DSP sau multiplicatori, PLL și alte componente sunt adesea construite în. Aici, în acest articol nu le voi examina.

Dezvoltatorul de proiect pentru FPGA-uri abstracte de obicei de la dispozitivul intern al unui cip specific. Pur și simplu descrie logica dorită pentru funcționarea cipului său "propriu" sub forma unei scheme sau a unui text pe Verilog / VHDL. Compiler știind structura internă a FPGA în sine încearcă să plaseze dispozitivul de circuit în funcție de blocuri logice configurabile disponibile și încearcă să se conecteze aceste blocuri folosind legături electronice programabile existente. În general, plasarea și urmărirea conexiunilor între blocurile logice din FPGA rămâne cu compilatorul.

Clasificarea FPGA prin tipul de stocare a configurației.

-SRAM Bazat.

Aceasta este una dintre cele mai comune soiuri de FPGA. Configurația FPGA este stocată în celule de memorie statice fabricate utilizând tehnologia standard CMOS.

Avantajul acestei tehnologii este posibilitatea reprogramării multiple a FPGA-urilor. Dezavantaje - nu cea mai mare viteză, după ce porniți firmware-ul de putere trebuie să fie încărcate din nou. Mijloacele de pe placa ar trebui să fie în continuare un bootloader, un chip special sau un microcontroler FLASH - toate acestea cresc costul produsului final.

Pe bază de Flash.

În astfel de jetoane, configurația este stocată în memoria FLASH internă sau memoria EEPROM. Astfel de FPGA-uri sunt mai bune deoarece firmware-ul nu dispare atunci când alimentarea este oprită. După punerea în funcțiune, microcircuitul este din nou pregătit pentru funcționare. Totuși, acest tip de FPGA are dezavantajele sale. Implementarea memoriei FLASH în interiorul cipului CMOS nu este foarte ușoară. Este necesar să se combine două procese tehnice diferite pentru producerea unor astfel de microcircuite. Deci, ele sunt mai scumpe. În plus, astfel de jetoane, de regulă, au un număr limitat de cicluri de rescriere a configurației.

Antifuse.

O tehnologie specială pentru care sunt realizate FPGA-uri programabile unice. Programarea unui astfel de FPGA este topirea unor jumperi speciale în locurile potrivite ale chipului pentru a forma circuitul dorit.

Dezavantajul este că puteți să programați / să blocați cipul o singură dată. După aceea, nimic nu poate fi repetat. Procesul în sine nu este suficient de rapid. Dar există o mulțime de avantaje ale unor astfel de FPGA-uri: acestea sunt destul de rapid (pot opera la frecvențe înalte), este mai puțin predispus la eșec în timpul radiații - toate datorită faptului că configurația este obținută sub formă de poduri, nu sub formă de logică suplimentară, la fel ca în SRAM pe bază de .

Blocuri logice configurabile.

Documentația lui Alter conține expresia Logic Array Block (LAB), o serie de logică. Plăcile FPGA ale lui Xilinx au aproximativ aceleași blocuri - bloc logic configurabil (CLB). Blocul logic configurabil - un element de bază al FPGA, există o anumită funcție logică simplă este realizată sau rezultatul calculului în registrele de stocare (flip-flops) pot fi efectuate.

Complexitatea și structura blocului logic configurabil (CLB) este determinată de producător.

Teoretic, un bloc logic configurabil poate fi, de exemplu, foarte simplu, pur și simplu ca un tranzistor separat. Sau poate fi foarte complicat, ca un întreg procesor. Acestea sunt punctele extreme ale realizării.

În primul caz, va fi necesar un număr mare de conexiuni programabile, pentru a asambla circuitul necesar de la fiecare tranzistor. În cel de-al doilea caz, este posibil să nu existe prea multă nevoie de o legătură, dar flexibilitatea proiectării unei scheme de utilizator este pierdută.

Este bloc, prin urmare, configurabil în mod tipic este un ceva între: este de obicei destul de complicat pentru a fi capabil de a fi cusute la o funcție, dar, de asemenea, suficient de mic pentru a găzdui o multitudine de blocuri în FPGA și pentru a fi în măsură să le lega într-un singur sistem.

Astfel, alegerea structurii unui bloc logic configurabil de către producătorul FPGA este întotdeauna o căutare a compromisului asupra zonei cristalului, a vitezei, a consumului de energie și așa mai departe.

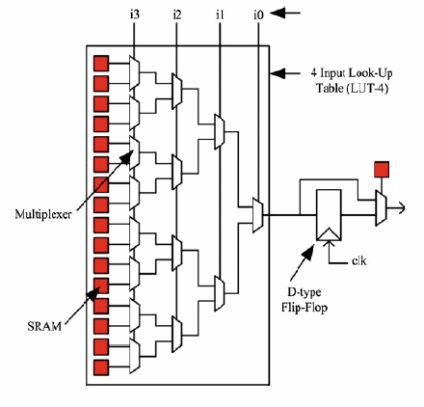

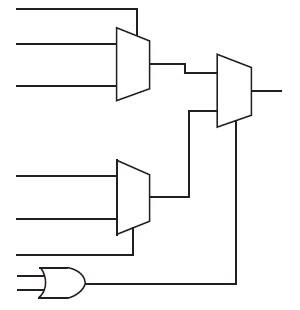

Un bloc logic configurabil poate consta din unul sau mai multe elemente logice de bază. În literatura de limbă engleză este elementul logic de bază (BLE) sau pur și simplu elementul logic (LE). FPGA-urile folosesc de obicei așa-numitele elemente logice de bază bazate pe LUT. Ceva de genul acesta:

Fig. 1. Un exemplu de element logic de bază tradițional.

LUT este o tabelă de căutare, un tabel de conversie. De exemplu, Figura 1 prezintă un LUT pe patru biți în blocul logic de bază. Aici un număr pe patru biți la intrarea funcției logice este asociat cu un rezultat de un bit. Pătraturile roșii din Fig. 1 reprezintă un element programabil, registrul este memoria unde este stocată firmware-ul pentru FPGA. Se vede că sunt necesare 16 configurații LUT pentru configurarea unui LUT pe 4 biți. Conținutul acestor registre definește o funcție logică implementată în elementul logic de bază.

Un alt registru de configurare (în Fig. 1 este un singur pătrat roșu dreapta) determină dacă la ieșire o poartă logică de bază care emite direct din LUT valoare sau să fie emise înscrisă în D-flip-flop cu o LUT valoare. Fixarea și stocarea datelor în circuite digitale este necesară în aproape orice proiect.

Având în vedere Fig. 1, ca exemplu al unui element logic de bază tradițional, înțelegeți ce redundanță este încorporată în cristalul modern al FPGA (bazat pe SRAM). Într-adevăr, de fapt, registrele de configurare (cutii roșii) nu sunt direct disponibile pentru a fi utilizate într-un proiect digital. Ele servesc numai pentru a forma o funcție personalizată. Pentru un D-flip-flop, proiectul utilizatorului necesită mai mult de 16 (uneori multe mai multe) declanșatoare pentru a stoca configurația FPGA.

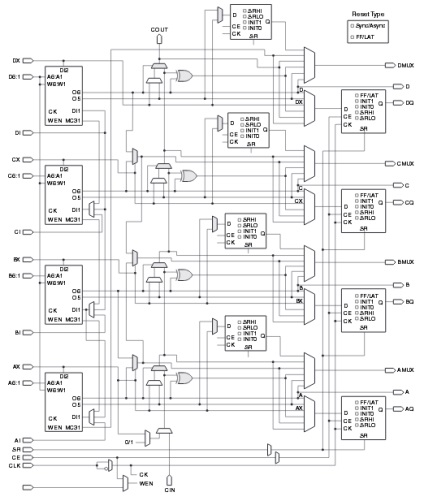

De fapt, elementul logic de bază în diferite FPGA-uri este mult mai complicat decât cel prezentat în Fig. 1. Mai jos sunt câteva exemple din documentația pentru diferite tipuri de FPGA.

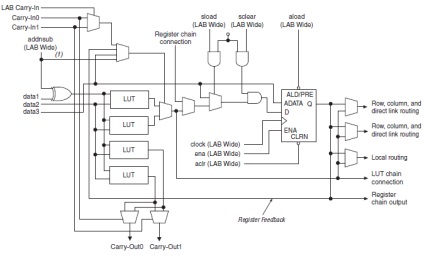

Fig. 2. Elementul logic de bază CPLD MAX II al Alterei.

Aici, LUT și D-Triggerul stocării rezultatelor sunt vizibile. Mai jos, în Fig. 3 prezintă elementul de bază al ciclonului III.

Fig. 3. Elementul logic de bază FPGA Cyclone III al Alterei.

În chips-urile Altera într-un LAB poate conține 10-16 LE.

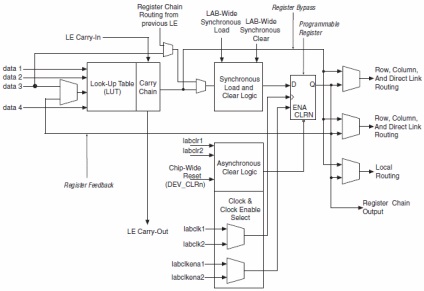

În chips-urile lui Xilinx Virtex-6, elementul logic de bază este așa-numitul Slice. Într-un CLB doar două felii. Dar un fel este un dispozitiv destul de complicat:

Fig. 4. Elementul de bază al Xilinx Virtex-6 Slice.

Într-un CLB Virtex-6 există 8 LUT și 16 D-Triggers și încă un lucru în acest sens. Deci, totul este complicat.

Cealaltă extremă este chips-urile FPGA ale Microsemi (fostă Actel).

De exemplu, în seria 40MX, elementul logic de bază arată astfel:

Fig. 5. Modulul Logic al seriei Microsemi 40MX.

Opt intrari si o iesire.

Nu există o masă de căutare, nici măcar un D-Trigger. Declanșatoarele, ca și restul logicii, se formează acolo unde este necesar din astfel de cărămizi minuscule - modulul logic.

De ce diferite companii au o diferență atât de mare în implementarea elementului logic de bază? Se pare că în chipsurile Microsemi conexiunea dintre unitățile de bază este mult mai ieftină: seria 40MX este o singură dată programabilă. În acesta, interconexiunile leagă "siguranța" între căile de conectare și nu pot fi modificate mai târziu. Nu există registre pentru stocarea temporară a firmware-ului. Nu există comutatoare programabile, multiplexoare, ca în FPGA de alte tipuri. Chipsurile Microsemi sunt un caz special. Această tehnologie se numește antifuză - pentru producerea unor astfel de microcircuite este utilizată o tehnologie modificată a procesului CMOS cu straturi suplimentare pentru organizarea conexiunilor interblocate.

Comunicări programabile între blocurile logice.

Pentru FPGA ne-a câștigat circuitul digital de dorit, nu este suficient, trebuie să configurați blocurile logice disponibile într-un mod special, în continuare nevoie pentru a crea, de comunicare de program, între blocuri logice.

În acest scop, există întrerupătoare special configurabile în FPGA.

În documentația în limba engleză, se întâlnesc următorii termeni: Arhitectura de rutare FPGA și Interconectarea programabilă de rutare. Este vorba despre asta, despre legăturile programabile între blocurile logice.

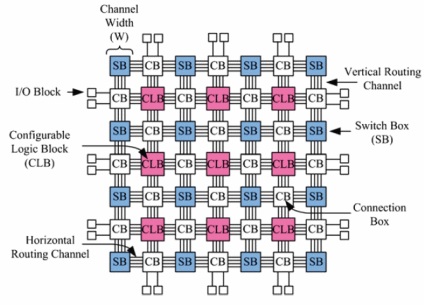

Există două metode principale pentru construirea FPGA pe baza tipului de arhitectură de comunicare: insulă și ierarhică.

Fig. 6. Insula FPGA.

O insulă FPGA este numită așa, deoarece blocurile configurabile sunt toate egale unele cu altele și sunt, ca și insulele din ocean, între nodurile de comutare și liniile de comunicație.

Aici, în Fig. 6 sunt notate cu CB - Box Connection și SB - Switch Box. În esență, acestea sunt multiplexoare programabile care conectează un CLB sau altul cu alt CLB prin firele din FPGA.

Acesta este un FPGA în stil insulă sau un FPGA bazat pe plasă. Un exemplu tipic de astfel de chips-uri este seria Altera Cyclone și Stratix.

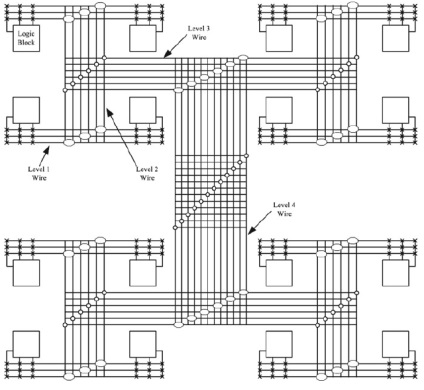

Al doilea tip cunoscut de FPGA este un FPGA ierarhic. Aici există un calcul în care există întotdeauna zone din schemă care interacționează mai strâns una cu cealaltă decât cu module la distanță ale proiectului.

Fig. 7. FPGA ierarhică.

Aici, CLB-urile din apropiere sunt destul de ușor de conectat, nu aveți nevoie de multe întrerupătoare și conexiunile rezultate funcționează rapid. Aici, dacă aveți nevoie de un bloc mai mare de calculatoare, atunci semnalul ar trebui să meargă la un nivel superior al ierarhiei și apoi să meargă adânc în următoarea "cameră".

Nu se poate spune că acest lucru este mult mai rău decât stilul insulei. Pur și simplu, fiecare metodă are argumente pro și contra.

Reprezentanții tipici ai FPGA-urilor ierarhice sunt chips-urile Altera ale seriei Flex10K, APEX.

Software pentru proiectarea FPGA.

Software-ul pentru proiectarea FPGA, și anume compilatorul (sintetizator de logică și instalator și asamblator) - aceasta este probabil cea mai dificilă parte a întregii tehnologii FPGA.

Compilatorul ar trebui să analizeze proiectul utilizatorului (scheme și descrieri de text pe Verilog HDL sau VHDL) și să genereze o listă netlist (o listă a tuturor elementelor de schemă și conexiunea dintre ele). Lista netlist ar trebui optimizată - funcțiile logice trebuie să fie minimizate, eventualele registre duplicate trebuie șterse.

Apoi compilatorul ar trebui să conțină toată logica din netlist în arhitectura FPGA existentă. Acest lucru este realizat de un instalator. El alocă elemente logice și legături dintre acestea (locul și traseul). Dificultatea este că același proiect poate fi plasat în FPGA în multe feluri și aceste metode sunt milioane. Unele destinații de plasare și de urmărire sunt mai bune, altele sunt mai rău. Principalul criteriu pentru calitatea sistemului primit este frecvența maximă la care proiectul va putea să funcționeze cu aranjamentul de elemente dat și cu această urmă de legătură. Aceasta este afectată de lungimea conexiunilor dintre blocurile logice și de numărul de comutatoare programabile între ele.

Compilatorul, cunoscând arhitectura FPGA prin rezultatele muncii, emite, de asemenea, un raport privind timpul de trecere a semnalelor de la registru la înregistrare. Aceste informații sunt adesea utile pentru dezvoltatorii de sisteme de înaltă performanță. Dezvoltatorul pentru FPGA poate da sfaturi compilatorului unde, în ce loc al cristalului este mai bine să plasați unul sau alt modul al proiectului.

Alegerea pentru proiectul său, pentru placile de bază specifice FPGA, dezvoltatorul într-o anumită măsură cade în dependență de producătorul acestui FPGA, deoarece el trebuie să utilizeze software-ul de la același producător.

Compania de software Altera: Quartus II.

Software Xilinx pentru proiectarea pentru FPGA: ISE Suite, Vivaldo Design Suite.

Despre compania Microsemi: Libero IDE, Libero SoC.

Probabil, software-ul, compilatoarele pentru FPGA sunt cea mai importantă componentă a proprietății intelectuale a companiilor producătoare de FPGA.