Planificatorul ia decizii pe baza priorității actuale a firului, care poate fi mai mare decât cea de bază. Există mai multe situații în care este logic să creșteți prioritatea unui fir.

De exemplu, după terminarea operației I / O, prioritatea fluxului este mărită pentru a permite pornirea mai rapidă a acestuia și, probabil, inițierea unei operații I / O din nou. În acest fel, sistemul încurajează firele interactive și sprijină dispozitivele I / O ocupate. Suma cu care crește prioritatea, nu este documentată și depinde de dispozitivul (valori pentru disc și CD recomandat - este 1, pentru rețea - 2, tastatura și mouse-ul - 6 și placa de sunet - 8). În viitor, în câteva intervale de timp, prioritatea scade treptat la cea de bază.

Alte exemple de astfel de situații sunt: trezirea firului după starea de așteptare a semaforului sau a altui eveniment; fluxul de acces la intrarea ferestrei.

Creșterea dinamică a priorității rezolvă, de asemenea, problema firelor de repaus care nu primesc acces la procesor pentru o lungă perioadă de timp. După ce ați detectat astfel de fluxuri, reporniți timp de aproximativ 4 secunde. Sistemul își ridică temporar prioritatea la 15 și le dă două cuante de timp. Un efect secundar al aplicării acestei tehnologii poate fi soluția problemei cunoscute a inversiunii prioritare [Tanenbaum]. Această problemă apare atunci când un fir cu prioritate mică deține o resursă, blocând fire cu prioritate ridicată care revendică această resursă. Soluția constă în creșterea artificială a priorității sale de ceva timp.

Creșterea dinamică a priorităților are rolul de a optimiza lățimea totală a sistemului, dar nu toate aplicațiile beneficiază de el. Puteți dezactiva îmbunătățirea dinamică a priorității utilizând funcțiile SetProcessPriorityBoost și SetThreadPriorityBoost.

Amploarea cuantumului timpului

Amploarea cuantumului timpului este esențială pentru funcționarea eficientă a sistemului în ansamblu. Este necesar să se păstreze calitățile interactive ale sistemului și, în același timp, să se evite prea multe schimbări de contexte. Probabil, valoarea optimă cuantică (o fracțiune de secundă) ar trebui să furnizeze servicii fără a comuta cererea utilizatorului, care ia procesorul pentru o scurtă perioadă de timp, după care generează de obicei o cerere I / O. În acest caz, costurile de expediere sunt reduse la minimum și sunt furnizate timpi de răspuns acceptabili.

Alegerea între valorile scurte și lungi se poate face folosind panoul "Proprietăți" din "Computerul meu". Valoarea cuantică este setată în valoarea registru HKLM \ SYSTEM \ CurrentControlSet \ Control \ PriorityControl \ Win32PrioritySeparation.

- Care este prioritatea relativă a unui fir?

A doua componentă a priorității globale a firului este prioritatea relativă a firului individual. Trebuie subliniat că prioritatea clasei este asociată cu procesul, iar prioritatea relativă este cu firele individuale din cadrul procesului. Debitul poate fi una dintre cele șapte priorități posibile: Idle, Lowest, Below Normal, Normal, Above Normal, Highest or Time Critical, timp).

Tabelul 5.2. Prioritățile relative ale firului

- Care este "prioritatea dinamică" a firului?

Multe sisteme de operare oferă posibilitatea schimbării priorităților în timpul duratei de viață a fluxului. O schimbare prioritară poate apărea la inițiativa firului însuși atunci când se ocupă de un apel corespunzător la sistemul de operare sau la inițiativa utilizatorului atunci când execută comanda corespunzătoare. În plus, OS în sine poate schimba prioritățile fluxurilor, în funcție de situația care se dezvoltă în sistem. În acest din urmă caz, prioritățile sunt numite dinamice, spre deosebire de prioritățile imuabile și fixe.

- Conceptul de cache și cache.

Memoria cache este o memorie de mare viteză alocată unui singur cip cu un procesor sau extern de procesor. Cache-ul servește ca un tampon de mare viteză între CPU și o memorie principală relativ lentă. Ideea cache-ului se bazează pe prezicerea celor mai probabile rezultate ale procesorului în RAM. Această abordare se bazează pe principiul localității temporale și spațiale a programului.

Dacă CPU accesează un obiect de memorie RAM, procesorul va reveni în curând la acest obiect cu o mare probabilitate de succes. Un exemplu al acestei situații poate fi codul sau datele în cicluri. Acest concept este descris de principiul localității temporale, conform căruia obiectele de memorie operativă folosite frecvent trebuie să fie "mai aproape" de CPU (în memoria cache).

Pentru a reconcilia conținutul memoriei cache și al memoriei RAM, folosiți trei metode de scriere:

· Scrieți prin - memoria este actualizată simultan cu memoria cache.

Buffered write through - informațiile sunt întârziate în memoria cache înainte de a fi scrise în memoria principală și rescrise în memorie în acele cicluri atunci când CPU-ul nu o accesează.

· Write back - bitul schimbării este utilizat în câmpul tag-ul și linia este rescrisă în memoria RAM numai dacă bitul de schimbare este 1.

De regulă, toate metodele de înregistrare, cu excepția trecerii, permit creșterea performanței și amânarea operațiunilor de scriere în RAM.

În structura memoriei cache se disting două tipuri de blocuri de date:

· Memorie de afișare a datelor (de fapt, datele în sine, duplicate din memoria principală);

· Memorie de etichete (semne care indică locația datelor cache în RAM).

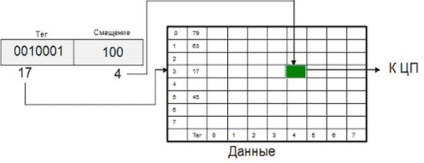

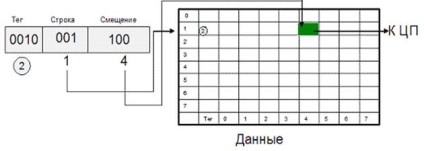

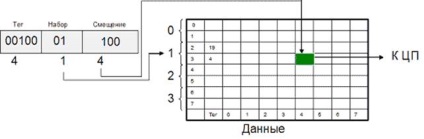

Spațiul de memorie pentru afișarea datelor în memoria cache este împărțit în rânduri - blocuri de lungime fixă (de exemplu, 32, 64 sau 128 octeți). Fiecare linie de cache poate conține un bloc octet aliniat continuu din memoria principală. Blocul RAM care este mapat la această linie de cache este determinat de eticheta de linie și de algoritmul de afișare. Conform algoritmilor pentru afișarea memoriei RAM, trei cache-uri sunt alocate cache-ului:

cache complet asociativ;

cache de afișare direct;

multiple cache asociat.

Unul dintre principalele avantaje ale acestei metode de afișare este utilizarea bună a RAM-ului, Nu există nicio limită în care blocul poate fi mapat la o anumită linie de cache. Dezavantajele includ implementarea hardware complexă a acestei metode necesită o cantitate mare de circuite (în principal comparatoare), care mărește timpul de acces pentru o astfel de cache, și de a crește costul său.

14. Fig. Schema organizării cache-ului în MP Motorola MC68020

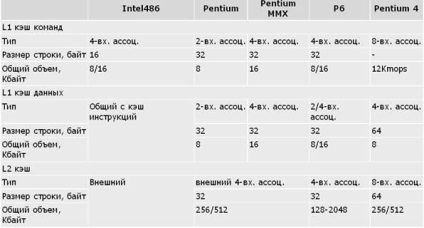

Acest algoritm de cartografiere combină avantajele ambelor cache complet asociativă (buna utilizare a memoriei, de mare viteză), și acces cache direct (simplitatea și ieftinătate) doar ușor inferior acestor caracteristici ale algoritmului original. De aceea, cache-ul asociativ multiplu este cel mai răspândit (caracteristicile cache-ului subsistemului CAC-1 de masă).

Tabel. Caracteristicile subsistemului cache din procesorul IA-32

Note: Intel-486 utilizează o singură memorie cache de comenzi și date de primul nivel. În Pentium Pro L1, memoria cache este de 8 Kbytes cu 2 intrări asociative, în celelalte modele P6 16 Kbytes cu 4 intrări asociative. În Pentium 4, în loc de cache-ul de instrucțiuni L1, se utilizează cache-ul L1 al micro-operațiilor (memoria cache).

Pentru a organiza memoria cache, puteți utiliza arhitectura Princeton (memorie cache pentru comenzi și date, de exemplu, în Intel-486). Această soluție evidentă (și inevitabilă pentru sistemele von Neumann cu cache extern bazată pe cache) nu este întotdeauna cea mai eficientă soluție. Separarea cache-ului în cache-ul de instrucțiuni și cache-ul de date (memoria cache a arhitecturii Harvard) vă permite să îmbunătățiți eficiența cache-ului din următoarele motive:

Mulți procesori moderni au o arhitectură în care conductele de transport funcționează în paralel. Astfel, selectarea comenzii și accesul la datele de comandă se realizează în diferite stadii ale conductei, iar utilizarea unei cache-uri separate permite efectuarea acestor operații în paralel.

· Cache-ul de instrucțiuni poate fi implementat numai pentru citire, prin urmare nu sunt necesare algoritmi de scriere, ceea ce face acest cache mai ușor, mai ieftin și mai rapid.

De aceea, toate cele mai recente modele IA-32, începând cu Pentium, utilizează arhitectura Harvard pentru a organiza memoria cache de nivel 1.

Criteriul pentru o funcționare eficientă a cache-ului poate fi considerat ca reducerea timpului mediu de acces la memorie în comparație cu un sistem fără memorie cache. În acest caz, timpul de acces mediu poate fi estimat după cum urmează:

15. Tcp = (Thit x Rhit) + (Tmx x (1 Rhit))

în care Thit - timpul de acces la memoria cache în cazul contactului (include timp pentru a-identifica un dor sau lovit), Tmiss - timpul necesar pentru unitatea de sarcină din memoria principală în linia de cache, în cazul unui dor cache și livrarea ulterioară a datelor solicitate la procesor, Rhit - frecvența loviturilor.

Evident, cu cât valoarea lui Rhit este mai apropiată de 1, cu atât este mai mare valoarea Tcp pentru Thit. Frecvența hiturilor este determinată în principal de arhitectura cache-ului și volumul acestuia. Influența prezenței și absenței memoriei cache și a volumului acesteia asupra creșterii performanței CPU este prezentată în Tabelul. Dimensiunea și eficiența memoriei cache

Tabel. Dimensiunea și eficiența memoriei cache

Complexitatea acestui mecanism este influențată în mod semnificativ de

O strategie de plasare care determină locul în care se află memoria cache

ar trebui să plasați fiecare bloc din memoria principală.

În funcție de modul în care sunt alocate datele de memorie principale, există trei tipuri de memorie cache în memoria cache:

· Cache cu afișare directă (plasare);

· Cache complet asociativ;

· Cache asociat multiplu sau memorie cache parțial asociativă.

Un tip multi-asociativ sau un tip parțial asociativ de cartografiere este unul dintre compromisurile posibile care combină meritele metodelor directe și asociative. Cache-ul (și etichetele și datele) este împărțit într-un număr de module. Dependența dintre modul și blocurile OD este la fel de rigidă ca și în cazul cartografierii directe. Dar plasarea blocurilor pe liniile modulului este arbitrară și se folosește un principiu asociativ pentru a găsi linia dreaptă în cadrul modulului. Această metodă de afișare este cea mai utilizată în microprocesoare moderne.

- Ce determină eficiența cache-ului.

- De ce am nevoie de TLB (tampon de asociere a traducerii).

cel mai recent. O schemă simplificată TLB este prezentată în Fig. 5. Tampon de asociere pentru traducere.

Pentru a găsi pagini care nu sunt în TLB, managerul de memorie virtuală utilizează tabele de pagini create programat. Conceptual, tabelul de pagini este prezentat în Fig. 3 Diagrama conceptuală a tabelului de pagini.