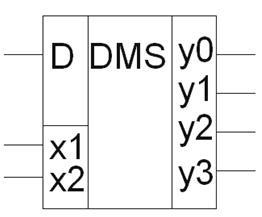

O diagramă schematică a multiplexorului este prezentată în Fig. 25, b.

În acele cazuri în care este necesară transmiterea datelor de intrare pe mai multe biți în formă paralelă cu ieșirile, se folosește multiplexarea paralelă a multiplexorilor cu numărul de biți din datele transferate.

y0 = x1 * x2 * D, y2 = x1 * x2 * D,

y0 = x1 * x2 * D, y0 = x1 * x2 * D.

Utilizarea unui demultiplexor poate simplifica în mod semnificativ construirea unui dispozitiv logic având mai multe ieșiri, pe care se formează diferite funcții logice ale acelorași variabile.

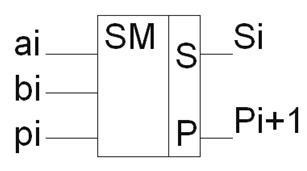

SUMMATOR BINAR SINGUR-TIMP.

Din principiul discutat anterior numerelor binare plus multibit că în fiecare dintre biții produse de același tip de acțiune: figura este determinată de suma modulo 2 a numerelor și termeni din bitul transporta de intrare este format și transferat, transmis următoarea cifră. Aceste acțiuni sunt implementate printr-o sumă binară cu un singur bit. Reprezentarea simbolică a unui astfel de adder este prezentată în Fig. 27, a. Are trei intrări pentru a da cifrele cifrelor termenilor ai. bi și transferul pi; la ieșirea sumă se se formează. și un transfer pi + 1, i destinat transmisiei la următoarea cifră.

Într-un adder de o singură cifră, pot fi furnizate intrări pentru a furniza atât valori directe ale cifrelor termenilor ai. bi și transferul valorilor pi și inverse, precum și ieșirile pe care se formează valorile inverse ale variabilelor de ieșire.

Tabelul 6 prezintă legea privind funcționarea unui numărător de o singură cifră.

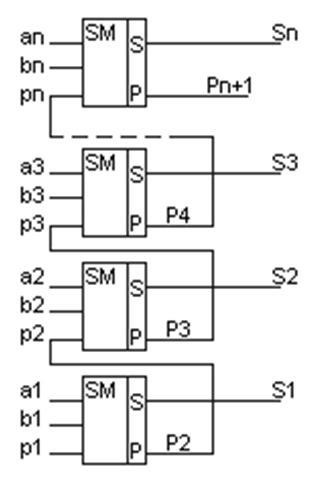

SUMMATORI BINARI MULTI-DISCHARGE.

În funcție de metoda de introducere a biților summands, sumatorii sunt împărțiți în două tipuri: acțiuni secvențiale și paralele. Sumatoarele primilor biți de tip în secvența de numere introduse clorhidric formă, m. E. Digit prin cifre (LSB forward), sumatoarele de al doilea tip, fiecare dintre componentele alimentate la forma para paralel, adică. E. Toate evacuările simultan.

Totalizatorul acțiunii secvențiale. Constă dintr-o singură cifră

a ieșitorului, ieșirea pi + 1 a cărei ieșire pi este conectată la intrarea pi printr-un element de întârziere, parametrii căruia se potrivesc cu rata biților care se descarcă la intrările adderului. Operația de însumare în toți biții termenilor se efectuează utilizând același adder cu un singur bit, dar secvențial în timp, începând cu cifrele de ordin inferior. O astfel de construcție a adderului este posibilă datorită faptului că termenii apar într-o formă secvențială.

Avantajul evident al sequencerului secvențial este cantitatea mică de echipament necesar pentru a-l construi. Cu toate acestea, necesitatea asociată de procesare secvențială a descărcărilor conduce la o viteză extrem de scăzută. Prin urmare. Sumele de acest tip sunt utilizate în prezent foarte rar.

Totalizator al acțiunii paralele. Se compune din curse separate, fiecare dintre ele conținând o singură cifră (Figura 28).

Când se dau termeni, cifrele cifrelor lor ajung la un coeficient corespunzător de o cifră. Fiecare din odnorazryad sumatoare-TION generează la ieșirile sale suma de descărcare cifre prezente corespunzătoare și transferul transmis la intrare sumator odnorazryad-TION dintre următoarele descărcare (mai mari).

O astfel de organizare a procesului de organizare a transferului, numit transfer secvențial, reduce viteza totalizatorilor multi-biti, deoarece rezultatul în bitul de înaltă ordine al adderului se obține numai după finalizarea propagării transferului în toate cifrele.

Măriți viteza add-on-urilor paralele. Pentru a asigura o viteză mare, distribuitoarele paralele trebuie construite pe elemente cu viteză ridicată.

În cel mai nefavorabil caz, transferul care are loc în categoria low-order poate provoca secvențial transferuri în toți ceilalți biți. În acest caz, timpul de transfer t = t1 * n, unde t1 - timpul de propagare a propagării într-o singură serie de timp.

Scăderea t este obținută prin următoarele metode.

1. În construcția de sumatoare circuite de un bit tind să reducă numărul de elemente din circuit între intrare, care primește un impuls de transfer și pi randament, care generează Xia transmise următorului impuls de descărcare de transfer pi + i.

2. În circuitele de la pi la pi + 1, se utilizează elemente cu o viteză crescută.

3. Circuitele de sumare trebuie construite astfel încât semnalele de ieșire ale fiecărui element logic din circuitul de la pi. la pi + am primit de la cel mai mic număr posibil de alte elemente logice, din moment ce unește fiecare element-ment suplimentar al unui anumit transfer de lanț punct, de obicei, are drept rezultat o capacitate parazitare, lungirea fronturile de semnal, și, prin urmare, o creștere a întârzierii de propagare a semnalului și reducerea vitezei adderului.

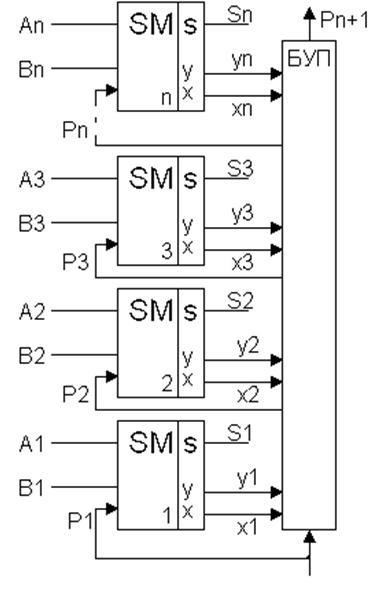

4. Dispozitivele aplicabile pentru formarea transferurilor în formă paralelă. În cazul prezentat în Fig. Un sumator 29 printr-un dispozitiv numit un proces accelerat de unitate de transfer de formare a Produ transferurile ditsya în formă paralelă, adică. E. O singură dată pentru toate evacuările. Transferurile din acest bloc merg simultan la toate totalizatoarele de biți. Atunci când acest bit viperei nu conțin lanțuri ale transporta, acestea sunt cote-miruyut numai cantitatea de Si și cantitatea de Yi și Xi, pentru transferurile-Koto ryh sunt necesare. Aceste valori Xi și Yi sunt necesare pentru carry în blocul de transport accelerat, acestea descurajează-fisionabile următoarele situații: Yi = 1 înseamnă că, în i-lea cu descărcare Renos pe-pi + 1 la următorul (p + 1) bit -lea este necesar pentru a forma indiferent de sosirea într-o anumită descărcare de gestiune a transferului din categoria anterioară; Xi = 1 înseamnă că la cifra i transferul pi + i ar trebui să fie format numai în condiția sosirii transferului pi. de la nivelul precedent:

Yi = a1 * b1; X1 = (al + b1) * p1.

Valorile Xi și Yi sunt formate simultan în toate sumatoare bit, simultan la intrările unității de transfer accelerate de rulare, și, prin urmare, în acest bloc generează simultan un bit de transport alimentat la sumatoarele. După primirea transferurilor din blocul de transfer condiționat, sumele Si se formează în sumatorii de descărcare de gestiune.

Deoarece elementele logice care alcătuiesc CCC sunt comutate cu o întârziere de tad. apoi o schimbare în non-timp, care combinație de semnale de intrare semnalele de ieșire ale dispozitivului (dacă acestea variază în rezultatul acestei re-) valori vor fi stabilite numai după fenomenele tranzitorii de capăt ale elementelor logice-corespun- de funingine. Pe drumul de la intrările dispozitivului la ieșirile sale, elementele logice individuale sunt conectate în serie. Prin urmare, durata proceselor tranzitorii va depinde de numărul elementelor logice care sunt incluse într-un astfel de lanț. PRIMA-nyaemaya Metoda tzad în prezent pentru determinarea unei elemente logice care furnizează utilizări, disponibilitatea lanțurilor incluse în măsurarea fiecare alte elemente logice similare permite evaluarea întârzierea generală într-un lanț de întârziere suma elementelor logice individuale. La evaluarea bystrodey-Corolar KTSU necesare pentru identificarea lanțului de porți între dispozitivele de intrare și de ieșire, Koto-cerul se va stabili cea mai mare întârziere, iar întârzierea este pliat între elementele logice ale tsepoch-ki. Acesta conține, de obicei, cel mai mare număr de elemente logice introduse unul după altul de la intrările la ieșiri. Dar pot exista excepții, legate, de exemplu, de prezența în lanțul mai scurt a elementelor logice individuale inerțiale cu taz mare. Prin urmare, în cazul general, este necesar să analizăm toate lanțurile elementelor logice de la intrările la ieșiri și să identificăm cel care dă cea mai mare întârziere.

CUPRINS ÎN KCU.

Întârzierea neuniformă a trecerii semnalului în părțile individuale ale KCU este uneori asociată cu "concursuri" în viteza de comutare a elementelor logice. Ca urmare a acestui fenomen, ieșirile anumitor elemente pot avea un zgomot de impuls. În unele cazuri, întârzierea inegală în trecerea semnalului în lanțuri separate de elemente logice poate duce la o interferență pulsată și la ieșirea CCU. Vom arăta acest lucru cu un exemplu.

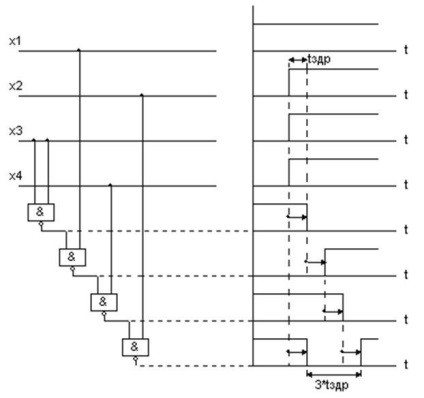

Luați în considerare CCC din fig. 30, a. Semnalul de intrare este schimbat cu codul de cod 1000 1111. Întârzierea în fiecare tzad element de logica. Schema structurală a KCU și diagramele de timp pentru acest exemplu sunt prezentate în Fig. 30, b. În acest caz, ieșirea KTSU schimba codul de intrare sig-1000 Nala cod scurt 1111 este setat la zero (la ora 3 * tzdr), cu toate că condițiile de funcționare ale valorii de ieșire a fost păstrată la nivelul unității.

Acest lucru rezultă direct din graficele de sincronizare, dacă neglijăm întârzierile de comutare de elemente logice, atunci când durata interferenței depășește o anumită valoare, este posibil să se Rushen conectat la dispozitivele KTSU de sănătate de ieșire (declanșatoare, contoare, și așa mai departe. D.). În astfel de cazuri, "concursurile" se numesc "periculoase".

Pentru a combate "concursurile periculoase", puteți lua măsuri diferite. În primul rând, uneori este posibil să se furnizeze o astfel de ordine de schimbare a codurilor de intrare, în care nici un zgomot de impuls nu va apărea deloc la ieșire, fie durata lor va scădea la o valoare sigură. În cazurile necesare, o astfel de întârziere poate fi introdusă în mod artificial prin includerea unui lanț de număr par de invertoare. În al doilea rând, în sinteza CCC corespunzătoare, uneori este posibil să se găsească o astfel de variantă a formulei structurale (și, în consecință, a schemei structurale), în care este posibil să se reducă mărimea zgomotului de impuls.

În astfel de cazuri, "concursurile" se numesc "periculoase". Pentru a combate "concursurile periculoase", puteți lua măsuri diferite. În primul rând, uneori este posibil să se furnizeze o astfel de ordine de schimbare a codurilor de intrare, în care nici un zgomot de impuls nu va apărea deloc la ieșire, fie durata acestora va scădea la o valoare sigură. În cazurile necesare, o astfel de întârziere poate fi introdusă în mod artificial prin includerea unui lanț de număr par de invertoare. În al doilea rând, în sinteza CCC corespunzătoare, uneori este posibil să se găsească o astfel de variantă a formulei structurale (și, în consecință, a schemei structurale), în care este posibil să se reducă amploarea zgomotului de impuls.

În al treilea rând, este posibil să se organizeze transferul sincron al semnalelor de la un dispozitiv la altul. În acest scop, sunt introduse impulsuri speciale de sincronizare, care specifică momentele de transfer de informații între dispozitive individuale. Pauza dintre impulsurile de sincronizare poate fi aleasă astfel încât în timpul perioadei sale să se termine tranzitorii și să se stabilească valori staționare la ieșirile dispozitivelor.

Transferul sincron al informațiilor în dispozitivele digitale moderne este utilizat foarte mult. Această problemă a fost deja discutată anterior, de exemplu, atunci când se analizează contrapartidele tipice, inclusiv multiplexoarele. Rețineți că prezența "contestațiilor" și a zgomotului impulsului rezultat afectează fiabilitatea dispozitivelor digitale.