Înmulțirea numerelor în formă binară este similară cu multiplicarea în sistemul numeric zecimal. După cum ne amintim de la cursul școlii, este mai ușor să se înmulțească într-o coloană. La implementarea acestui algoritm, este necesară multiplicarea fiecărei cifre a multiplicatorului cu cifra corespunzătoare a multiplicatorului.

De exemplu, luați în considerare multiplicarea a două numere binare pe patru biți. Permiteți-i să se înmulțească numărul 10112 (1110) cu numărul 11012 (1310). Ca rezultat al multiplicării, ne așteptăm să obținem numărul 100011112 (14310). Executăm operația de multiplicare într-o coloană din sistemul binar, așa cum se arată în Figura 15.10.

Figura 15.10 - Efectuarea unei operații de multiplicare într-o coloană

Pentru a forma o lucrare, este necesar să se calculeze patru produse parțiale. Vă rugăm să rețineți că, în aritmetică binară este necesară pentru a realiza multiplicarea numai numerele 0 și 1. Acest lucru înseamnă că trebuie să rezume un deînmulțit la suma produselor parțiale rămase sau nu. Ca urmare, pentru formarea de produs parțial puteți utiliza elemente logice „2i“, conectat la fiecare cifră binară de deînmulțit.

Pentru a forma un produs parțial, cu excepția înmulțirea cu un singur bit, este necesar să se efectueze o deplasare la stânga de numărul de biți care corespund factorului de greutate al descărcării. Schimbarea poate fi realizată prin simpla conectare a biților corespunzători ai produselor parțiale la biții necesari ai agregatului binar.

Pentru o diagramă schematică a multiplicatorului a fost similar cu algoritmul înmulțirii binare, este prezentată în figura 14.10 folosim în mod condiționat cipuri grafice, în care intrările sunt aranjate puncte de sus și de jos. Acest lucru este permis de GOST. În conformitate cu algoritmul de multiplicare într-o coloană, avem nevoie de trei agregate pe patru biți.

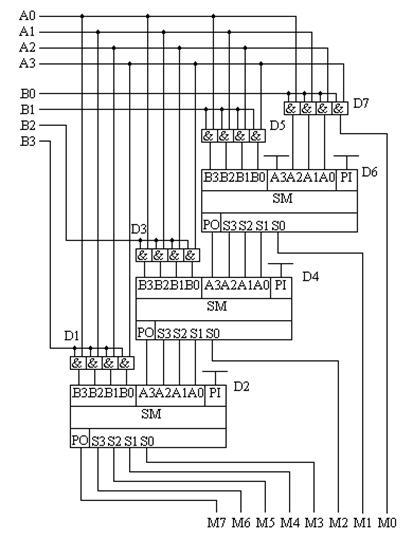

Schema de bază a multiplicatorului, care realizează algoritmul de multiplicare binară într-o coloană, este prezentată în Figura 15.11.

Formarea produselor parțiale în schema prezentată în Figura 15.11 se realizează prin microcircuite digitale D1, D3, D5 și D7. În aceste jetoane, într-un singur corp, există patru elemente logice "2I".

Adderul, realizat pe chipul D6, însumează primul și cel de-al doilea produs privat. Ordinea inferioară a primului produs parțial nu trebuie să fie însumată (a se vedea Figura 15.11). Prin urmare, acesta este alimentat direct la ieșirea multiplicatorului (bit M0).

Al doilea produs parțial trebuie deplasat cu o singură cifră. Aceasta se realizează prin faptul că bitul de ordine scăzut al numărului de ieșire al adaosului D6 este conectat la a doua cifră a produsului (M1). Dar atunci primul produs particular trebuie să fie deplasat cu o singură cifră în stânga față de cel de-al doilea produs particular!

Figura 15.11 - Diagrama schematică a multiplicatorului matricei 4'4

Această operație aritmetică este realizată astfel încât LSB grupul de intrare A este conectată la un prim produs de descărcare privat, primul grup de descărcare intrările A conectat la al doilea lucrărilor private de descărcare de gestiune, etc. Cu toate acestea, cel mai înalt rang al grupului de intrări A nu are nimic de conectat!

Pentru a rezolva această contradicție amintesc că, dacă vom scrie la stânga numărului de zero, valoarea numărului inițial nu se va schimba, așa că avem acest bit este conectat la sistemul de sârmă comun, adăugând astfel un zero în cel mai semnificativ bit din primele lucrări private.

În exact același fel, al treilea și al patrulea produs privat sunt însumate la rezultat. Această operație este efectuată de chips-urile D4 și, respectiv, D2. Spre deosebire de construcția schemei este numai în faptul că nu este nevoie să se gândească la cea mai semnificativă cifră a sumei anterioare, deoarece cipul anterior vipera generează un semnal de transport pentru cip ulterioare.

Privind atent la circuitul de multiplicare prezentat în figura 14.11 se poate vedea că aceasta formează matricea formată de lanțurile care transporta cifre ale lui A și B. Numărul de puncte de intersecție a acestor circuite sunt elemente logice „2i“. Din acest motiv, multiplicatori puse în aplicare în cadrul acestui sistem sunt cunoscute ca multiplicatori matrice.

Viteza circuitului prezentată în Figura 14.11 este determinată de timpul maxim de propagare a semnalului de-a lungul celei mai lungi căi. Aceasta este calea care trece prin chips-urile D7, D6, D4, D2. Funcționarea în circuit timp poate fi redusă, în cazul în care nu sumatoare aranjate succesiv, după cum se presupune algoritmul din figura 14.10, și suma produselor parțiale în perechi, apoi însumate perechi de produse parțiale, etc. În acest caz, timpul operației de multiplicare va fi mult redus.

Se remarcă în special câștigul de performanță în construirea multiplicatorilor multi-cifre. Cu toate acestea, nimic nu este gratuit. În schimbul unei creșteri a performanței va trebui să plătească o creștere a capacității totalizatorilor și, prin urmare, complexitatea schemei. Dacă totalizatorii produselor parțiale rămân cu aceeași capacitate numerică ca înainte, atunci totalizatorii de perechi de produse parțiale trebuie să fie multiplicați cu unul.

viperei Bit cvadruple produse parțiale este sumator de biți doi biți mai mare de produse parțiale, deoarece însumarea celor patru numere ale valorii în cazul cel mai defavorabil poate fi crescut de patru ori, etc.

Multiplicatorii matrice digitale sunt utilizate pe scară largă în sistemele de procesare a semnalului pentru schimbarea dispozitivului raport de transmisie, pentru realizarea de convertizoare de frecvență, și ca o componentă a filtrelor digitale.

Acum, ia în considerare următorul bloc, nu mai puțin frecvent utilizat în circuitele și semnalele de procesare digitală. Acestea sunt dispozitive de memorie permanente.