de control a funcționării cache la nivel de pagină

În paginile elementelor catalog și tabelele de pagini sunt de 2 biți, care sunt utilizate pentru a controla procesorul de semnal de ieșire și de a participa la pagini de cache.

CPD biți (CPD = dezactivează 1) sau permite (CPD = 0) punerea în cache a paginii. caching Interzicerea necesară pentru paginile care conțin porturile I / O pentru cartografiere de memorie. De asemenea, este util pentru pagina cache, care nu obține în viteză, de exemplu, paginile care conțin programul de inițializare.

bit PWT determină modul în care actualizarea memoriei cache RAM și externă (nivelul 2 cache). PWT = 1. În cazul în care datele sunt determinate pentru a scrie-prin cache cu la PWT = 0 este utilizat în pagina metoda writeback corespunzătoare. Este folosit în microprocesoare de la Pentium. Deoarece cache internă - memorie MP i486 funcționează cu scriere prin intermediul, starea PWT bit nu este afectat. biți PWT, în acest caz, acționează numai asupra cutiei de viteze exterior.

Asigurarea coerenței de cip de memorie cache în sistemele multiprocesor

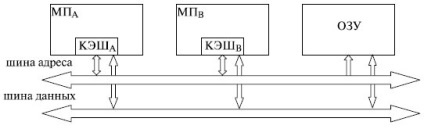

Luați în considerare caracteristicile cache-memorie în cazul în care mai multe procesoare au o memorie comună (fig. 4.4). În acest caz, este posibil să apară probleme cu cache informații din memoria cache a - memoria microprocesorului.

Fig. 4.4. Sistemul multimicroprocessor Structura cu RAM partajată

Să presupunem că unii au crezut MP Un rând de date din memoria RAM la manualul său intern și a schimbat datele în această linie în timpul operației.

Am observat că există două mecanisme de bază de upgrade de memorie:

Pentru a asigura mecanisme de coordonare (coerență) hardware de memorie utilizate în sistemele multiprocesor. permițând să rezolve această problemă. Astfel de mecanisme sunt numite protocoale de memorie cache coerenta. Aceste protocoale sunt proiectate pentru a se asigura că orice citire a elementului de date returnează ultima dată înregistrat în valoarea sa.

Există două clase de protocoale de coerență:

În sistemele multiprocesor cu memorie partajată cele mai populare protocoale de observare. deoarece starea memoriei cache studiu, ei pot folosi conexiunea fizică existentă - un autobuz de memorie.

Două metode de bază utilizate pentru a menține coerența.

O înregistrare alternativă de protocol de la anularea este de a actualiza toate copiile elementului de date, în cazul înregistrării în elementul de date.

Acest tip de protocol este numit un protocol cu actualizarea înregistrării (protocolul de actualizare de scriere), sau intrările de traducere de protocol (protocol de difuzare scriere).

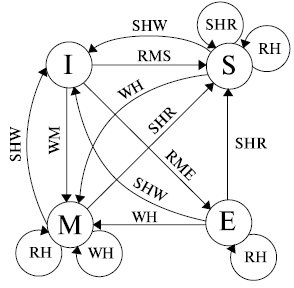

Luați în considerare una dintre cele mai comune protocoale oferă funcționarea coordonată a cache-memorie de mai multe microprocesoare și o memorie principală în sistemele multimicroprocessor, protocolul mesi. care face parte din monitorizarea protocolului cu anularea. Ne face cunoștință cu ei sistemul de exemplu, procesor dual format din microprocesoare A și B.

Acest protocol utilizează bara de stare a caracteristicii cache 4-memoria microprocesorului, primele litere se numesc protocol:

- stare alterată (Modificat): informațiile stocate în memoria cache a microprocesorului O semnificativă numai în cache; este absent în memoria principală și memoria cache a altor procesoare;

- copie exclusivă (Exclusiv): informațiile conținute în memoria cache și, încă mai conține doar o memorie;

- informațiile partajate (Shared): informațiile conținute în cache A este conținută în memoria cache, cel puțin un alt MP și o memorie RAM;

- Informații nesigure (nevalid): în linia de cache este informații nevalide.

Astfel, caracteristicile de procesare a protocolului de stat mesi reflectă următoarea condiție (în raport cu IPA) memorie cache rând (vezi Tabelul 4.2.):

Tabelul 4.2. Caracteristicile de formare mesi de protocol de stat

protocol de conectare Stare

În timpul funcționării, microprocesor A, în ceea ce privește următoarele situații de memorie sunt posibile coerență:

- RH (Read Hit) - cache lovit atunci când citesc;

- WH (Scrie Hit) - cache lovit atunci când scrieți;

- RME (Citește ra Exclusiv) - cache dor atunci când citesc;

- RMS (citire ra Shared) - cache dor atunci când citesc, dar blocul corespunzătoare este în cache-ul unui alt CPU;

- WM (Scrie ra) - cache dor atunci când scrieți;

- SHR (Snoop Hit Read) - detectarea copie bloc atunci când ascultați o altă operație de citire cache;

- SHW (Snoop Hit Scriere) - detectare bloc copie operație de scriere când ascultați un alt cache.

Cel mai mare interes aici sunt ultimele două poziții.

Unitatea indicația se schimbă starea în cache-MP de memorie, în funcție de diferite situații în munca sa și sistemul multimicroprocessor de lucru în ansamblu sunt prezentate în Fig. 4.5.

Fig. 4.5. Mesi-chart asigura cache coerentei

Noi ilustra câteva dintre conversiile prezentate.

Atunci când această linie în starea cache-memorie luate în considerare microprocesor se va schimba de la partajat la modificat (Shared).

Dacă o memorie cache de linie de memorie a fost în stare nevalidă. adică, informația în ea era falsă, atunci în ceea ce privește această linie ar trebui să fie luate în considerare doar o situație asociată cu ratări cache. Deci, dacă a existat o memorie cache dor atunci când efectuați o operație de scriere, linia necesară va fi introduse în cache - memoria MP, datele modificate, și va primi statutul de proprietar exclusiv al noilor informații (Modificat) vor fi înregistrate în această linie.

Scurte rezultate. Se ocupă de curs cu principiile generale de funcționare a cache-memoria microprocesorului, cache organizație de memorie cu mapare directă, complet asociativă și set-asociativ KP. Principalele mecanisme de actualizare a memoriei: cache-through și scrie-back. Prezentat organizarea cache-memoria internă a microprocesorului. Dezasamblat modalități de a asigura coerența procesoare cache-memorie în sistemele multiprocesor.