Primul și primar caracteristica de chips-uri CMOS este o rezistență de intrare mare a acestor circuite. Ca urmare a intrării de cip CMOS poate fi indus orice stres, inclusiv egală cu jumătate din tensiunea de alimentare, și stocate pe ea suficient de mult timp. Atunci când este aplicat CMOS intrare jumătate cip tranzistori de putere sunt deschise în partea superioară și în brațul inferior al circuitului de ieșire etapă, rezultând cip CMOS începe să consume inacceptabil de mare curent și se poate deteriora. [3] Concluzie: Intrările de circuite integrate CMOS digitale, în orice caz, nu poate fi lăsat neconectat!

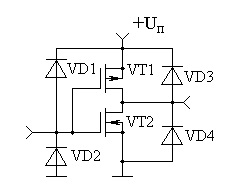

A doua caracteristică a chips-uri CMOS este faptul că acestea pot lucra cu putere off. Cu toate acestea, ei lucrează mai des decât greșit. Această caracteristică se datorează structurii circuitelor etapă CMOS de intrare. Schema circuitului complet al unui invertor CMOS prezentat în figura 4.7.

Diodele VD1 și VD2 sunt introduse pentru a proteja etapa de intrare a defalcării de electricitatea statică. În același timp, atunci când sunt aplicate la intrarea CMOS circuite integrate cu potențial ridicat-l prin dioda VD1 va ajunge pe autobuz cip de putere, și așa cum se consumă destul de un curent mic, cipul CMOS va începe să funcționeze. Cu toate acestea, în unele cazuri, acest lucru poate să nu fie suficientă energie pentru puterea cip. Ca urmare, un cip CMOS poate funcționa defectuos. Concluzie: Manipularea incorectă a circuitelor CMOS, verificați cu atenție cip de putere. în special concluziile carcasei. Atunci când slab cositorite puterea de ieșire negativă a potențialului său va fi diferită de capacitatea totală a circuitului de sârmă.

A treia caracteristică de chips-uri CMOS asociate cu diode parazitare VD3 și VD4, care poate fi perforat când sursa de alimentare este conectat incorect (chips-uri TTL rezista la sursa de alimentare polaritate de moment). Pentru protejarea CMOS ICS polaritate circuitul de alimentare trebuie prevăzută o diodă de protecție.

A patra caracteristică a CMOS chip mdash curent pulsul curge în circuitul de alimentare atunci când comută de la starea de zero la singular și vice-versa. Ca urmare a trecerii de la chips-uri TTL analog CMOS cip dramatic crește nivelul de zgomot. În unele cazuri, este important, și este necesar să se renunțe la utilizarea de cipuri CMOS în beneficiul circuite TTL sau BICMOS.

Nivelurile logice de chips-uri CMOS

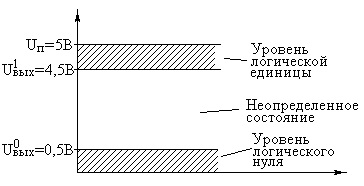

CMOS niveluri de logica chips-uri diferă semnificativ de nivele ale circuitelor logice TTL. Atunci când nici o tensiune de sarcină la ieșirea cip CMOS coincide cu tensiunea de alimentare (logica un nivel) sau potențial conductor comun (nivel logic zero). Când curentul de sarcină crește tensiunea unităților logice pot scade la 2.8V (Us = 15 V) a tensiunii de alimentare. Nivelul admisibila de tensiune la ieșire de circuite CMOS digitale (ICS seria K561) la putere pyativoltovom este prezentată în figura 4.8.

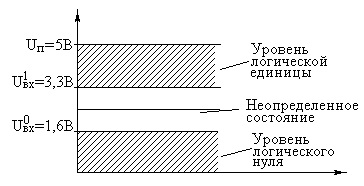

Așa cum am menționat mai devreme, tensiunea de intrare ICS digitale, în comparație cu un randament de permis în mod normal în limite largi. Pentru CMOS chips-uri au fost de acord cu 30% din stocul. Limitele unui nivel logic zero și unități pentru cipuri CMOS la putere pyativoltovom sunt prezentate în Figura 4.9.

Când reducerea logica zero a tensiunii și logica se poate determina granița în același mod (divizat de alimentare 3).