decodoare de funcții și codificatoare sunt clare din numele lor. Decodorul convertește un număr binar de intrare într-un semnal de ieșire (decriptează cod) encoder convertește semnalul de intrare într-un cod binar număr de ieșire (criptează numărul de intrare). Numărul de semnale de ieșire ale semnalelor decodor și traductorul de intrare să fie egal cu numărul de stări posibile ale codului binar (codul de intrare la decodor și codul de ieșire de la codificatorul), adică 2 n. unde n - cod binar bit (Figura 5.1.). decodoare Chip sunt indicate prin litere pe circuitele de curent continuu (de la decodorul limba engleză), și traductoarele cip - CD-uri (de la codorul în limba engleză).

Fig. 5.1. funcțiile decodoare (stânga) și traductorul (dreapta)

La ieșirea decodorului este întotdeauna prezent, doar un singur semnal, numărul de cod de intrare a semnalului este unic determinată. Codul de ieșire a semnalului de intrare encoder este unic număr determinat.

Să considerăm funcția de decodor.

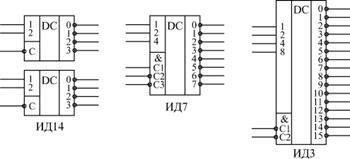

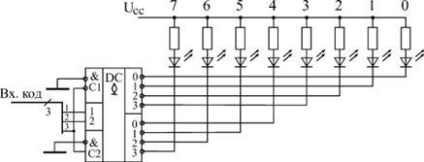

Fig. 5.2. Exemple decodoare chipset

Cod la intrările 1, 2, 4, 8, definește numărul de ieșire activ (intrare 1 corespunde LSB intrare codul 8 - următorul cod de cifre). Intrări autorizare C1, C2, C3 sunt combinate cu funcția ȘI și au polaritate indicate în desen. De exemplu, în tabelul. 5.1 arată tabelul de adevăr al ID7 decodor (3-8). Există, de asemenea, decodoare 4-10 (de exemplu, ID6), care este tratat, nu toate stările posibile ale codului de intrare 16, dar numai primele 10 dintre acestea.

Primele trei rânduri din tabel corespund de a interzice semnale de ieșire. Rezoluția de ieșire va intrare în unitate C1 și zerouri pe C2 intrările și C5. „X“ reprezintă un simbol condiție nu-mi pasă de această intrare (fie zero sau unu). Cele mai mici opt rânduri corespund rezoluția semnalelor de ieșire. numărul de ieșire activă (pe care se formează un semnal zero) este determinată de codul de pe intrările 1, 2, 4, și corespunde intrare 1 LSB cod și intrare 4 - următorul cod cifre.

Tabelul 5.1. Tabelul de adevăr al decodorului 3-8 (ID7)

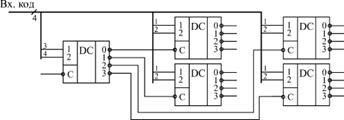

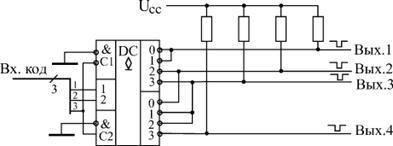

Cele mai tipice decodoarele aplicației constă în descifrarea introducerea codului, intrările de C sunt folosite ca semnale de control al stroboscopice. Număr de activ (adică zero) semnal de ieșire indică codul de intrare este introdus. Dacă doriți să decripta codul cu un număr mare de biți, este posibil să se combine mai multe decodoare chips-uri (un exemplu este prezentat în fig. 5.3).

Fig. 5.3. Creșterea numărului de biți de decodor

În acest cod de biți mai vechi sunt alimentate la decodorul de bază, care ieșirile sunt lăsate să lucreze mai multe decodoare suplimentare. În intrările combinate ale acestor decodoare sunt furnizate biți suplimentare semnificative ale codului de intrare. Dintre cele cinci 2-4 decodoare cip sunt disponibile decodor 4-16, așa cum se arată (deși este mai bine, desigur, gata să ia chip). În mod similar, nouă chips-uri puteți obține 3-8 decodor 6-64 și 4-16 din cele șaptesprezece chips-uri - decodor 8-256. O altă utilizare comună a decodoarelor - selecție (selecție) dat codurile de intrare. Apariția unui semnal negativ la ieșirea selectată a decodorului ar însemna admiterea la introducerea codului de interes. În acest caz, creșterea numărului de biți ai codului de intrare selectabile mult mai ușor decât în cel precedent (vezi. Fig. 5.3). De exemplu, două cipuri permit 4-16 au fost selectate cod de 8 biți (fig. 5.4). In exemplul din figura 16 selecteaza 2A codul Hex (binar 0,010 1010). Atunci când acest lucru este un decodor cu mai mici de patru biți de cod, iar celălalt - cu mai mari patru biți. Decodificatoare sunt combinate în așa fel încât una dintre ele permite celeilalte la intrările și -C1-C2. Aplicarea întrerupătoare mecanice decodoarele ieșiri (comutatoare, poduri), puteți schimba cu ușurință codul, selectabil de schemă.

Fig. 5.4. Selektirovanie decodoare cod

Fig. 5.5. Includerea decodorul ca demultiplexor

Ca și în orice alte circuite digitale, decodoare pentru situația cea mai critică este schimbarea simultană sau aproape simultană a semnalelor de intrare. De exemplu, în cazul în care porțile cu funcționarea vreodată permite decodorului, momentul de schimbare a codului de intrare false impulsuri negative, scurte pot apărea oriunde pe ieșirea decodorului. Acest lucru se poate datora fie biți de cod expozițională non-simultane (din cauza chips-uri de cod sursă imperfecte sau din cauza diferitelor întârzieri de propagare prin liniile de comunicație) și cu întârzierile interne decodoarele cipuri înseși.

Fig. 5.6. Gating semnalele de ieșire ale decodorului

În cazul în care astfel de impulsuri parazite ar trebui să fie excluse, este posibil să se utilizeze de sincronizare prin intermediul semnalelor de stroboscop. Așa cum se utilizează pentru acest semnal C, ar trebui să înceapă după codul de variație a curentului și codul de final până la următoarea schimbare, adică bucla imbricată trebuie să fie puse în aplicare. Fig. 5.6 arată cum va arăta ieșirea decodorului fără suprimare a fasciculului și dependente.

La al doilea nivel de reprezentare (un model cu întârzieri de timp) sunt, de asemenea, necesar să se ia în considerare faptul că întârzierea decodorul peste întârzierea de elemente logice simple, este aproximativ de două ori codul de intrare, și aproximativ jumătate - pentru intrările de poarta. Asta este, dacă încercați să înlocuiți circuitul decodor pe porți logice, un astfel de decodor se va transforma mai lent. Valoarea exactă a întârzierii este necesar să se uite în directoarele.

Fig. 5.7. indicarea pozițional pe ieșirile de decodoare cu OK

Decodoare cu ieșiri de OK (ID5, ID10), convenabil de a folosi în circuitele de afișare cu LED-uri de poziție. Fig. 5.7 prezintă un exemplu de afișare pe un cip ID5 care reprezintă două decodor 2-4 combinate cu intrări pentru alimentarea unui cod și porți care permit ușor de a construi decodor 3-8. În acest cod de cifre mai vechi selectează unul dintre decodoare 2-4 (zero corespunde la partea superioară a circuitului decodor, iar unitatea - jos). Aceasta este, în acest caz, numărul de LED-uri aprinse este egal cu decodorul de cod de intrare. Această indicație se numește pozitional.

Fig. 5.8. Combinarea decodoare cu ieșiri OK

ieșire cip de decodor cu UC pot fi combinate între ele pentru a implementa un fir OR (fig. 5.8). Zero pe ieșirea combinată va fi atunci când cel puțin una dintre ieșirile produse zero. La cod uniform de intrare build-pas (de exemplu, folosind un contor), o astfel de soluție permite formarea unei secvențe destul de complex de semnale de ieșire. Cu toate acestea, fiecare ieșire decodor poate fi folosit pentru a produce un singur semnal de ieșire. Acest lucru limitează capacitatea acestor circuite.

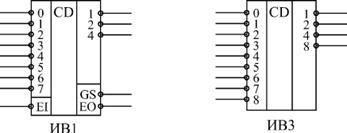

Codificatoare sunt utilizate mult mai puțin frecvent decât decodoare. Acest lucru se datorează unei mai specific domeniu de aplicare a acestora. Mult mai puțin alegere și encodere chips-uri din seriile standard. Interne encodere serie au o litere ale numelui IV.

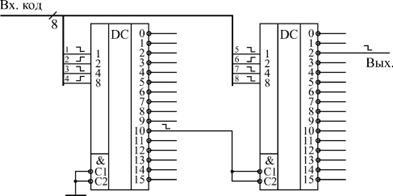

Fig. 5.9 prezintă un exemplu două cipuri codificatoare IV1 și IV3. În primul rând are 8 intrări și trei ieșiri (encoder 8-3), iar al doilea - 9 intrări și 4 ieșiri (encoder 9-4). Toate intrările codificatoare - inverted (semnale de intrare activă - zero). Toate ieșirile sunt de asemenea inversate, care este format prin codul invers. Circuit integrat IV1, pe lângă opt intrări de date și trei biți ai codului de ieșire (1, 2, 4) are un inversat permite introducerea -ei, sosire randament -GS caracteristică orice semnal de intrare, și transporta -EO ieșire, permițând combinarea mai multor codificatoare pentru a crește bit .

Fig. 5.9. codificatoare cip

Tabelul de adevăr al codorului prezentat în tabelul IV1. 5.2.

Tabelul 5.2. Tabelul de adevăr programatorul IV1

Tabelul arată că codul de ieșire 1, 2, 4 este format prin inversul numărului de cod binar al liniei de introducere pe care vine de intrare negativ. Atunci când mai multe primirea simultană a semnalelor de intrare care generează un cod de ieșire de intrare cu cel mai mare număr corespunzător, adică intrări mai mari au prioritate mai tineri. Prin urmare, aceasta se numește un codificator de prioritate. În absența semnalelor de intrare (a doua linie a tabelului) care generează un cod de ieșire 111. unică -ei semnal (prima linie) dezactivează codorul (toate ieșirile sunt setate la unul). La ieșire a produs -GS zero la sosirea unui semnal de intrare, ceea ce permite, în special, pentru a distinge sosirea situației de intrare zero, de la situația absenței oricăror semnale de intrare. Randamentul -EO devine activ (zero), atunci când nu există nici un semnal de intrare, dar permit operarea -ei semnalului traductorului.

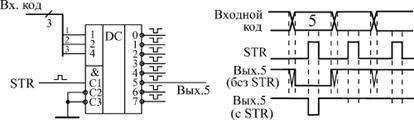

codificatoare de aplicare standard este de a reduce numărul de semnale. De exemplu, în cazul informațiilor codificator IV1 despre cele opt semnale de intrare este minimizat la trei ieșiri. Este foarte convenabil, de exemplu, la transmiterea semnalelor pe distanțe lungi. Cu toate acestea, semnalele de intrare nu ar trebui să vină în același timp. Fig. 5.10 prezintă schema standard, care încorporează codificator și graficul de funcționare de sincronizare.

Fig. 5.10. codificator includere standard

Inversoare cod de ieșire duce la faptul că la sosirea semnalului de intrare la zero este nenulă cod este generat la ieșire și codul 111, adică 7. În mod similar, la sosire, de exemplu, al treilea semnal de intrare este produs la ieșirea codului 100, adică 4 și cu sosirea a cincea ieșire - cod 010, adică 2.

Prezența EI codificatoarelor și intrările EO vă permite să crească numărul de intrări și descarcă codificator, dar cu elemente suplimentare la ieșire. Fig. 5.11 prezintă un exemplu de construcție a codorului 16-4 pentru două cipuri codificatoare IV1 și cele trei elemente 2I-NO (LA3).

Fig. 5.11. Encoder 16-4 pe cele două traductoarele 8-3

schimbarea simultană sau aproape simultană în semnalul de intrare encoder dă naștere la incertitudine în perioadele de ieșire. Codul de ieșire poate lua pentru scurt timp o valoare care nu se potrivește cu niciunul dintre semnalele de intrare. Prin urmare, în cazurile în care semnalele de intrare pot veni în același timp, este necesar să se sincronizeze codul de ieșire, de exemplu, prin intermediul EI semnal permisiv, care ar trebui să vină doar atunci când starea de incertitudine este de peste.

Întârzierea de la intrare la codul de ieșire codificator aproximativ jumătate ori întârzierea elementului logic și de întârziere înainte de GS - aproximativ două ori mai mare. Valoarea exactă a cip de întârziere este necesar să se uite în directoarele.