Întrebarea # 2 „Clasificarea microcontrolere“

Toate MC pot fi împărțite în trei categorii principale:

MK aplicații embedded de 8 biți;

16- și 32-biți MC;

procesoare de semnal digital (DSP).

procesor de semnal digital (DSP) - un procesor specializat pentru procesarea semnalului digital. Proprietăți: Harvard arhitectura de memorie construit cu acces aleator (eșantionare sincron mai multe cuvinte de mașini), punerea în aplicare a hardware-instrucțiuni complexe de procesare a semnalului digital (operație de exemplu, înmulțiți-se acumuleze 1 ciclu), bucle imbricate, o lungime destul de mare a transportorului.

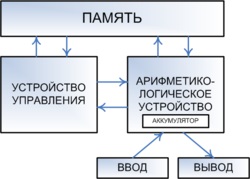

Arhitectura von Neumann - stocarea în comun a programelor și a datelor în memoria unui calculator (mai ieftin, dar mai lent). În general:

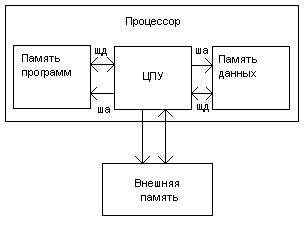

Arhitectura Harvard - software-ul și datele sunt stocate în diferite dispozitive de stocare (în arhitectura von Neumann pentru preluarea unei instrucțiuni și două operanzi necesare trei etape, există două, în realitate, de data aceasta poate fi redusă la un singur ciclu de ceas).

Întrebarea # 3 „Tendințe în dezvoltarea arhitecturii“

Întrebarea # 5 - „Prezentare generală a evenimentelor fluxului de control cu microprocesor“

Din punctul de vedere al schimbului de comenzi între procesor și memorie de toate computerele pot fi împărțite în patru clase:

SISD (Single Instruction Single Data) - «flux de instrucțiuni unic, fluxul de date unică„";

SIMD (Single Instruction Multiply date) - un singur flux de instrucțiuni, o mulțime de fluxuri de date;

MISD (Instruction Multiple date unică) - o mulțime de fluxuri de echipe, un flux de date;

MIMD (instrucțiuni multiple de date multiple) - o mulțime de echipe fluxuri o mulțime de fluxuri de date.

În forma cea mai generală a unui procesor multifir cuprinde două tipuri de primitivelor. Primul tip - este o resursă care susține fluxul de execuție, care se numește mutex (de la excludere reciprocă - «excludere reciprocă"), iar al doilea - eveniment. Aceasta este, atât fizic pus în aplicare un anumit mutex, în funcție de schema selectată - SMT sau CMP. În orice caz, procesul de implementare este de a se asigura că mutex următorul flux zahvatyvaaet la momentul execuției sale, iar apoi se dă. În cazul în care mutex este ocupat de un singur fir, al doilea fir poate dobândi. Procedura specifică pentru transferul de autoritate în posesia mutex de la un fir la altul poate fi întâmplătoare; aceasta depinde de punerea în aplicare a controlului, de exemplu, într-un anumit sistem de operare. În orice caz, managementul ar trebui să fie construit astfel încât resursele, constând din mutex, distribuite în mod corect și efectul copleșitor de incertitudine.

Evenimente - sunt obiecte (eveniment), de semnalizare a unei schimbări în mediul extern. Ele se pot traduce în modul de așteptare înainte de un eveniment sau un raport statutul lor la un alt eveniment. În acest fel, evenimentele pot interacționa unii cu alții, și în care trebuie să se asigure continuitatea datelor între evenimente. Asteptand agent de executare ar trebui să fie informat cu privire la disponibilitatea datelor pentru ea. Și, la fel ca în distribuția mutex trebuie să fie suprimat efectul de incertitudine, astfel încât atunci când se lucrează cu evenimentele ar trebui să fie suprimate prin efectul de necunoscut. SMT pentru prima dată sistemul a fost implementat în procesoarele Compaq Alpha 21464 precum și Intel Xeon MP si Itanium

Există dovezi suficiente pentru o declarație clară a beneficiilor CMP, comparativ cu SMT. Experiența de a crea procesoare de punere în aplicare SMT, este mult mai mare: de la mijlocul anilor '80 a făcut mai multe zeci de produse experimentale și mai multe procesoare de serie. Istoria CPM în timp scurt: dacă nu iau în considerare familia specifică de procesoare de semnal Texas Instruments TMS 320C8x, primul proiect de succes a fost Hydra, realizat la Universitatea Stanford. Printre proiectele universitare de cercetare care vizează construirea unei CMP-procesoare, cunoscut sub numele de trei - Wisconsin Multiscalar, Carnegie-Mellon Stampede și MIT M-mașină.

Niagara - «aliaj» MAJC și Hydra

Procesorul UltraSPARC T1, mai bine cunoscut sub numele de Niagara, două precursoare principale - Hydra și MAJC.

La mijlocul anilor '90, în urma Java procesoare specializate trageți de Sun Microsystems a fost o încercare de a crea un procesor cu un „cuvânt foarte lung» - Word instrucțiuni foarte lung (VLIW). Această inițiativă a fost numit MAJC (cu microprocesor Arhitectura pentru Java Computing). Ca și în alte proiecte, care a fost lansat la un moment dat (Intel IA-64 Itanium), în acest caz, sarcina a fost de a transfera o parte dintre operațiunile cele mai complexe în păstrarea compilator. tranzistor logic pot fi eliberate folosit pentru a crea unități funcționale mai productive (unități funcționale), pentru a asigura schimbul eficient de comenzi și date între CPU, memoria cache și memoria principală. Astfel, pentru a depăși „strangulare.“ Von Neumann

MAJC diferite de cele mai multe procesoare lipsesc coprocesoare specializate (subcontractanți), care sunt numite în mod obișnuit dispozitive funcționale pentru efectuarea operațiunilor întregi, plutitoare de date punct și multimedia. Ea toate unitățile funcționale sunt identice, capabile să execute orice operațiuni pe de o parte, a redus eficacitatea anumitor operațiuni, pe de altă rata de utilizare crescută a întregului procesor.

Niagara întruchipează cele mai bune dintre cele două abordări alternative pentru punerea în aplicare a multi-threading - SMT și CMP. La prima vedere, este foarte similar cu Hydra, ci mai degrabă poate fi numit Hydra Cascada «aspect». În afară de faptul că, în urmă - de două ori mai multe nuclee, fiecare dintre care se pot ocupa patru fire.

Abordarea proprie la crearea de procesoare multi-core oferite de IBM Cell al cărui proiect este numit „cip eterogenă multiprocesor» (eterogen cip multiprocesor). arhitecturii celulare, de asemenea, numit Cell Broadband Engine Architecture (CBEA). multiprocesor Cell este format din IBM 64-bit core arhitectura de putere și opt coprocesoare specializate care pun în aplicare schema de „o echipa o mulțime de date.“ În această arhitectură, IBM a numit unitatea de procesare sinergică (SPU).

Acesta poate fi un procesor separat flux (procesor Single streaming - SSP) și procesor multifir (Multi-Streaming Processor - MSP).

Reprezentanți ai matricei clasei procesoare SIMD indiscutabile considerate: ILLIAC IV, ICL DAP, Goodyear Aerospace MPP, mașină Racord 1 etc. În astfel de sisteme, un singur-guvernare consilii, dispozitivul monitorizează setul de prelucrare elemente de polițiști. Fiecare element de procesare primește de la dispozitivul de comandă în fiecare comandă fixă de timp aceeași mână și-l execută pe datele lor locale.

O altă clasă reprezentativă sunt procesoare SIMD-vector-LARG, care se bazează pe obrabotkadannyh vector. Vector de prelucrare crește performanța procesorului datorită faptului că prelucrarea întregului set de date (Age-torus), se face cu o singură comandă. calculatoare Vector ma matrice nipuliruyut de date similare în același mod ca și mașinile-ska polare prelucrează elementele individuale ale Insulelor Massey. În acest caz, este necesar să se ia în considerare fiecare element al vectorului ca un element de flux de date separat. Atunci când se lucrează în modul vector de procesoare vectoriale prelucrează datele aproape în paralel, ceea ce face de mai multe ori mai rapid decât atunci când funcționează în modul de scalare. Viteza maximă de transfer de date în format vectorial poate fi de 64 Gb / s, care este de 2 ordine de mărime mai repede decât mașinile de scalare. Exemple de acest tip de sistem este, de exemplu, procesoare firmele Hitachi si NEC

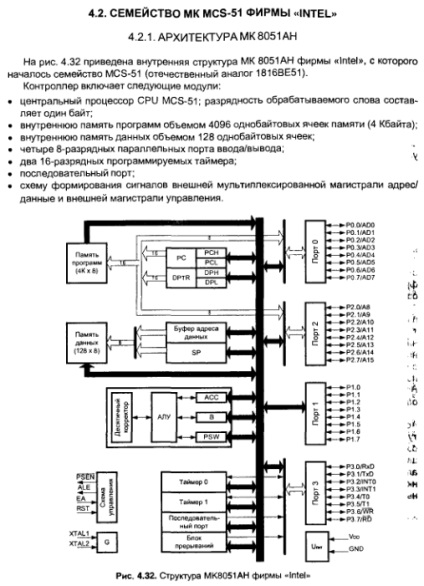

Întrebarea # 6 "un singur cip de computer micro-arhitectura MCS-51 familie"

Unitate de control (CU) generează semnale de control asupra autobuzelor la toate blocurile de instrucțiuni ale mașinii.

O unitate logică aritmetică (ALU) este proiectat pentru a efectua operații aritmetice și logice, informații de conversie. ALU, de obicei, este format din două registre, o viperă, și circuite de control. Sumatorul - efectuează plus alimentat la intrare de coduri binare. Registrele - celule de memorie rapide de diferite lungimi. circuitul de comandă primește instrucțiunile de peste semnalele de control de autobuz de la UC și de a le converti în semnale pentru controlul funcționării registrelor și vipera. ALU efectuează operații aritmetice (+, -, *, :) doar peste numere întregi binare.

Interfața de microprocesor.

selectarea din următoarele celule de instrucțiuni RAM și primirea unui registru de comandă;

decodificare Opcode;

citirea celulelor semnalelor de control ROM firmware care definesc procedurile pentru executarea unei operațiuni predeterminate și trimiterea de semnale de control la aceste unități;

înregistrarea rezultatelor din memorie.

Autobuzul circuit de control și porturile au următoarele funcții:

care primește informații de la port: gestionarea disponibilității portuare, statutul;

de organizare a canalului de transmitere a datelor între port și MP.

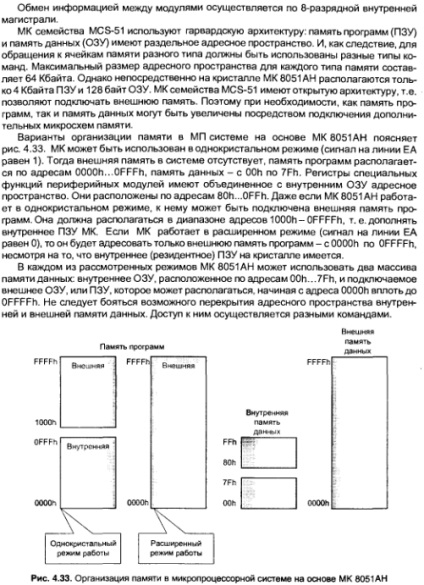

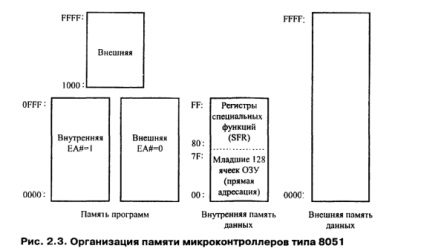

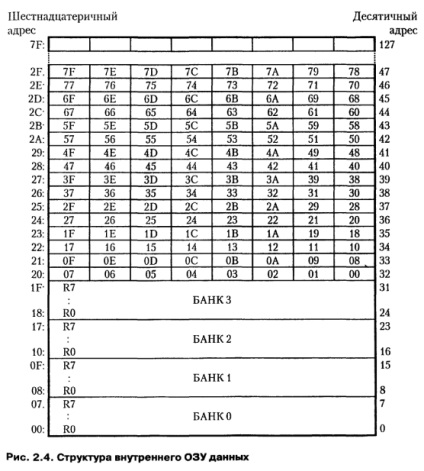

Întrebarea # 7 „Organizarea MS8-51 memoriei interne și externe“

oh

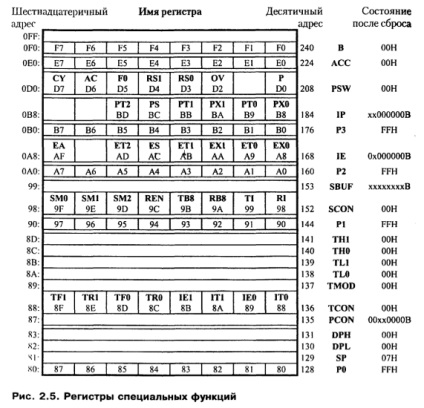

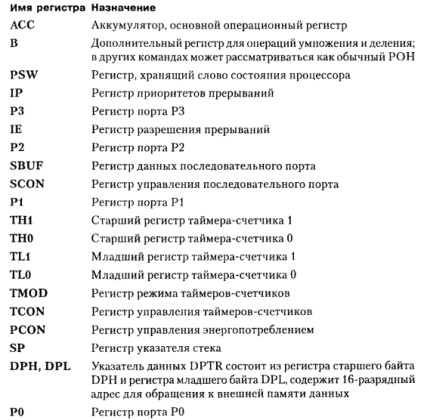

Figura 2.5 prezintă zona de registre de funcții speciale. Acesta include toate registrele de software disponibile (de control și de date) vnutrennihblokov IO.

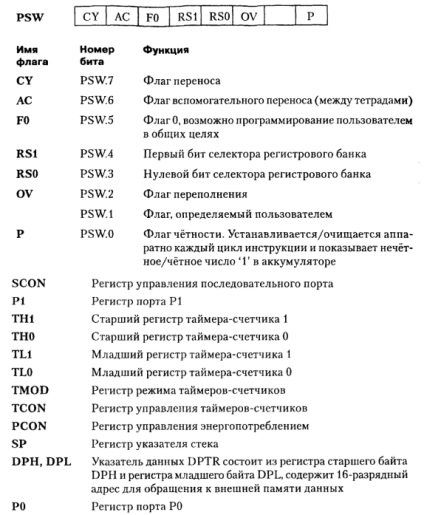

Formatul registrelor funcții speciale vor fi revizuite în secțiunile dedicate descrierii sistemului de întreruperi și blocurile individuale funcție de intrare-ieșire. Aici este formatul de PSW magazine registrului cuvântul de stare procesorului. Acest registru cu acumulatorul conține rezultatul execuției comenzii.

Formatul registrelor funcții speciale vor fi revizuite în secțiunile dedicate descrierii sistemului de întreruperi și blocurile individuale funcție de intrare-ieșire. Aici este formatul de PSW magazine registrului cuvântul de stare procesorului. Acest registru cu acumulatorul conține rezultatul execuției comenzii.

Întrebarea # 8 „porturi de intrare-ieșire MS8-51. Caracteristici ale programării. "