Acasă | Despre noi | feedback-ul

Chipsurile adder (engleză Adder), după cum sugerează și numele acestora, sunt destinate să însumeze două coduri binare de intrare, adică codul de ieșire va fi egal cu suma aritmetică a celor două coduri de intrare. De exemplu, dacă un cod de intrare este 7 (0111) iar al doilea este 5 (0101), atunci codul total la ieșire este 12 (1100). Suma a două numere binare cu numărul de biți N poate avea numărul de cifre (N + 1). De exemplu, când se însumează numerele 13 (1101) și 6 (0110), se obține numărul 19 (10011). Prin urmare, numărul de ieșiri ale divizorului este mai mare decât numărul de biți din codurile de intrare. Acest bit suplimentar (senior) se numește ieșirea de transfer.

În circuite, verile sunt notate cu literele SM. În seria internă, codul care indică IC a numărătorului este IM.

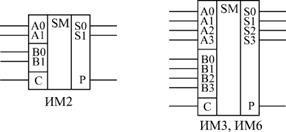

Totalizatorii sunt o singură cifră (pentru însumarea a două numere de o singură cifră), cele cu 2 biți (se adaugă numere de 2 cifre) și numerele de 4 cifre (adăugați numere de 4 cifre). Cea mai obișnuită utilizare este un adder de 4 biți. În Fig. 6.1 arată, de exemplu, adiții pe 2 și 4 biți. Microcircuitul IM6 diferă de IM3 numai de creșterea vitezei și de numărul pinilor utilizați ai microcircuitului, funcția fiind aceeași.

Fig. 6.1. Exemple de IC-uri suplimentare

În plus față de biții de ieșire ai sumei și a ieșirii transmisiei, add-urile au o intrare de extensie (un alt nume este intrarea de transfer) C pentru combinarea mai multor aditivi pentru a crește capacitatea de biți. Dacă se ajunge la o astfel de intrare, ieșirea este incrementată cu una, iar dacă nu se produce nici o valoare, ieșirea nu crește. Dacă utilizați un IC al adderului, atunci extensia sa C trebuie să fie zero.

De exemplu, în Tabelul. 6.1 prezintă tabelul complet al adevărului IM2 pe 2 biți. După cum se vede din tabel, codul de ieșire 3 biți (P, S1, S0) este egală cu suma codurilor de intrare 2 biți (A1, A0) și (B1, B0), și semnalul nivelul S. Zero - primul nivel inferior - superior . Tabelul cu adevărat complet al adderului pe 4 biți va fi prea mare, deci nu este dat. Dar esența lucrării rămâne exact la fel ca în cazul unui adder de 2 biți.

Sumatoarele pot fi de asemenea folosite pentru a însuma numerele în logică negativă (atunci când unitatea logică corespunde unui zero electric și invers, o unitate electrică corespunde unui zero logic). Dar, în acest caz, semnalul de intrare al transferului C devine și invers, deci atunci când se utilizează un cip de adunare la intrarea C, trebuie aplicată o unitate electrică (nivel de înaltă tensiune). Semnalul de ieșire al transferului P devine și invers, nivelul de tensiune scăzut pe el (zero electric) corespunde prezenței transferului. Adică, se dovedește că adderul funcționează exact în același mod cu logica pozitivă și negativă.

Tabelul 6.1. Tabela de adevăr a microcircuitului IM2 pe 2 biți

Să luăm în considerare un exemplu. Să presupunem că trebuie să adăugăm două cifre 5 și 7 în logica negativă. Numărul 5 în logica pozitivă 0101 corespunde codului binar, și în negativ - 1010. Numărul de cod 7 corespunde unui cod binar logica pozitivă 0111, iar în negativ - codul 1000. Atunci când este aplicat sumatorului codul de intrare 1010 (decimal 10 în logica pozitivă) și 1000 (decimal 8 logica pozitivă), obținem suma 10 + 8 = 18, adică codul 10010 în logica pozitivă. Dată fiind semnalul de intrare transporta C = 1 (nici o intrare de transport în logica negativă), ieșirea sumatorului va codifica pentru un mai mare: 18 + 1 = 19, adică 10011. Cu logica negativă va corespunde numărului 01100, adică 12 în absența producției carry . Ca rezultat, avem 5 + 7 = 12.

Adderul poate calcula nu numai suma, ci și diferența dintre codurile de intrare, adică funcționează ca un subtractor. Pentru a face acest lucru, numărul scăzut trebuie să fie pur și simplu inversat în biți și un semnal unic trebuie aplicat la intrarea de transfer C (Figura 6.2).

Fig. 6.2. Cu 4 cifre, pe impulsul IM6 și invertoarele LN1

De exemplu, să calculăm diferența dintre numărul 11 (1011) și numărul 5 (0101). Bitwise număr invertit 5 și se obține 1010, adică decimal 10. Sumatorul 11 când însumate dau 21 și 10, adică numărul binar 10101. Dacă semnalul C este egal cu 1, rezultatul este 10110 Discărcarea MSB (semnal de ieșire P) și se obține diferența 0110, adică 6.

Un alt exemplu. Să fie necesar să se calculeze diferența dintre numărul 12 (1100) și numărul 9 (1001). 9 bitwise invert obține 0110, adică zecimală 6. Găsiți totalul de 12 și 6, obținem 18, iar cu C = 1, obținem 19, adică un binar 10011. Cele patru LSB au 0,011, adică o zecimală 3.

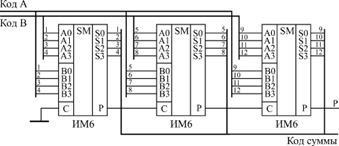

Cascading adders pentru a crește adâncimea de biți este foarte simplu. Este necesar să se transmită un semnal de la ieșirea transferului procesorului de adunare a biților cei mai puțin semnificativi la intrarea transferului adderului care procesează cele mai înalte cifre (Figura 6.3). Când cei trei aditivi pe 4 biți sunt combinați, se obține un adaos de 12 biți, care are o al 13-lea număr suplimentar (ieșirea transferului P).

Fig. 6.3. Cascadarea totalizatorilor IM6 pentru creșterea capacității de biți

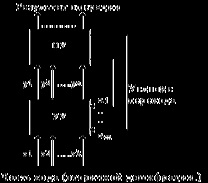

Stări nesigure asupra ieșirilor adderului pot apărea cu orice schimbare a codurilor de intrare (Figura 6.4). Codul de ieșire al sumei poate lua pentru o perioadă scurtă de timp valori care nu au legătură cu codurile de intrare, iar impulsurile parazitare scurte pot apărea la ieșirea transferului. Aceasta se datorează în primul rând unei schimbări non-simultane a biților codurilor de intrare. Pentru a evita influența acestor stări incerte asupra circuitului suplimentar, este necesar să se asigure sincronizarea sau închiderea semnalelor de ieșire. Dar pentru aceasta este necesar să avem informații despre momentele de modificare a codurilor de intrare, care nu sunt întotdeauna disponibile.

Fig. 6.4. Stări nesigure privind ieșirile adderului când se schimbă codurile de intrare

Întârzierea totalizatorului IM6 de la intrările la ieșirile sumei este de aproximativ două ori mai mare decât întârzierea elementului logic și de la intrările la ieșirea transferului, de aproximativ 1,5 ori. Întârzierile adunării IM3 sunt mai mult de jumătate din IM6. Prin urmare, în schemele în care viteza este importantă, este mai bine să utilizați IM6. Acest lucru este deosebit de important atunci când cascadă pentru a crește capacitatea de biți, deoarece acolo întârzierile de chips-uri individuale sunt adăugate împreună. Mărimea exactă a întârzierilor ar trebui analizată în cărțile de referință.

Sistemul aritmetic-logic este un circuit de tip combinație care nu necesită semnale de ceas legate de timp pentru funcționarea acestuia. Rezultatul operației apare la ieșirea ALU după o întârziere egală cu suma întârzierilor elementelor logice care formează cel mai lung lanț din interiorul ALU. Datorită trecerii succesive a transferului prin toți biți de ALU, lungimea lanțului cel mai lung și, în consecință, întârzierea totală a ULE, crește proporțional cu lungimea sa. Aproximativ, întârzierea ALU pe 32 de biți va fi de 32 de ori mai mare decât întârzierea unei ALU cu un singur bit. Utilizarea schemelor speciale de transfer accelerat permite de câteva ori reducerea întârzierii ALU-urilor pe mai multe biți.

În general, o ALU multifuncțională include o parte de operare (OS) și o unitate de comandă (CU) care efectuează o decriptare secundară a codului de comandă și determină operația efectuată în ALU.

Figura 4.2. Structura ULE

Setul de operațiuni efectuate în UA trebuie să aibă o exhaustivitate funcțională. Pentru a asigura completitudinea funcțională a patru operații:

- accesul la memorie pentru scrierea / citirea datelor;

- creștere / scădere;

- comparație (realizează posibilitatea unui transfer condiționat);

- opriți dispozitivul.

În primii procesatori, numărul de operațiuni a fost limitat la șaisprezece, acum ajunge la câteva sute.

Numărul de operațiuni efectuate este o caracteristică importantă a ALU.

ULE pot fi clasificate în funcție de o serie de caracteristici enumerate mai jos.

Clasificarea prin metoda reprezentării datelor:

- cu virgulă fixă;

- cu virgulă plutitoare.

2. Clasificarea prin metoda de operare asupra operanzilor:

· ALU consecutive, în care fiecare operație este efectuată secvențial pe fiecare cifră;

· ALU paralel, operația se efectuează simultan cu toate biții de date;

· ALU consecutiv - paralel, unde cuvântul de date este împărțit în silabe, prelucrarea datelor este efectuată în paralel pe cifrele silabelor și secvențial pe silabe.

3. Clasificarea utilizării sistemelor numerice:

4. Clasificarea prin natura elementelor și ansamblurilor:

- bloc-pentru executarea operațiunilor aritmetice separate blocuri speciale sunt introduse în structura ALU, care permite procesul de procesare a informațiilor să fie efectuat în paralel;

- conveior în transportor Operația ALU este împărțită într-o secvență de micro-operații efectuate în aceleași intervale de timp (măsuri) în diferite etape ale conductei, ceea ce permite efectuarea unei operații pe fluxul operanților la fiecare ciclu de ceas;

- multifuncționale sunt unități universale de tip ALU care efectuează mai multe operații într-un singur dispozitiv. În astfel de ALU, trebuie să configurați această operație folosind opcode.

5. Clasificarea în funcție de caracteristicile de timp.

Conform caracteristicilor de timp, ULE sunt împărțite în:

- sincronă - în ALU sincronă, fiecare operație este efectuată într-un singur ciclu de ceas.

- asincronă - ALU non-clocked, care furnizează viteză mare, așa cum sunt efectuate pe circuite combinaționale.

6. Clasificarea în funcție de structura dispozitivului de comandă: