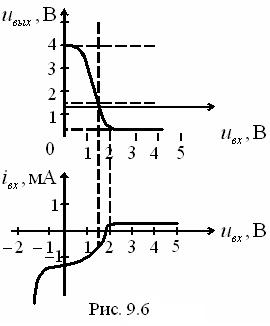

În Fig. 9.6 prezintă caracteristicile de transmisie și intrare interconectate. Graficele arată că, înainte de a ajunge la nivelul de prag al tensiunii de intrare la 1,5 V tranzistor VTN saturate, iar caracteristica de intrare este aproape liniară. Atunci când o tensiune negativă se aplică la stadiul de intrare, există o creștere bruscă a valorii absolute a curentului de intrare, ceea ce duce în cele din urmă la defalcare. În dispozitivele reale de protecție între emițător și sol include diodele de limitare.

Caracteristica de ieșire este relația dintre curentul de intrare și tensiunea de intrare. Luați în considerare această schemă pentru două stări logice pe ieșire. În Fig. 9.7 prezintă un circuit echivalent și o caracteristică tipică de ieșire a unui element logic deschis, adică element cu un semnal de 0 la ieșire. Curentul de 16 mA este maxim admis conform specificațiilor.

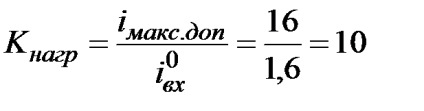

Factorul de sarcină determină numărul de intrări de elemente care pot fi conectate simultan la ieșirea unui element. Se știe că pentru diferite stări ale unui element logic curentul de intrare are o valoare diferită :. a. Prin urmare:

Numărul maxim de intrări pentru elementele TTL este de 8.

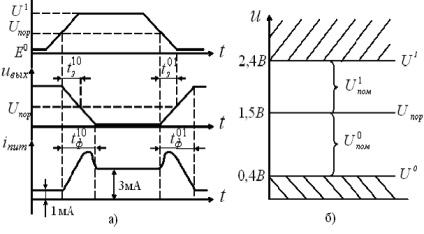

Caracteristicile dinamice reflectă tranzițiile atunci când schimbă stările elementelor logice. Acestea includ viteza, durata de pornire și oprire a elementelor, precum și imunitatea la zgomot.

Durata de pornire și oprire a elementelor este determinată de următoarele expresii:

.

Aici și - respectiv lungimea și în afara marginilor și și - respectiv semnalul de întârziere în timp ce trecerea elementului la 0 și 1. Prezența duratei proceselor de comutare cauzate de supraîncărcare de parazitare și capacitances inerția tranzistori. Acești parametri sunt prezentate în ris.9.9 asemenea.

Răspunsul este caracterizat de un timp mediu de întârziere:

.

Imunitatea de interferență este caracterizată prin parametrii arătați în fig. 4.9, b.

Opțiuni Circuite TTL cu suplimentare

În dispozitivele reale, sunt adesea folosite circuitele modernizate ale elementelor TTL cu caracteristici îmbunătățite și capabilități suplimentare. În Fig. 9.10 și este dată varianta circuitului invertor cu caracteristici de sarcină îmbunătățite.

Elementele logice de ieșire pot fi în trei stări: 0. 1 și z (impedanță sau starea off). Introducem elemente suplimentare în circuit, astfel încât elementul logic de bază să aibă starea z. Schema actualizată este prezentată în Fig. 4.14, b. Aici linia punctată reprezintă elemente noi. Dacă intrarea este 1. atunci elementul efectuează funcția 2N-NOT. Dacă intrarea este legată la pământ, atunci curentul colector al tranzistorului VTn este zero, toate tranzistoarele sunt închise, ieșirea este zero.