controler de memorie interfață ARHITECTURA SRAM pentru o performanță maximă a dispozitivului de comutare

Institutul de Cercetare pentru Studii de Sistem al RAS, ***** @ niisi. *****

Comutatoarele construite pe baza unei matrice de comutare oferă cea mai rapidă modalitate de comunicare a porturilor. Într-un astfel de comutator, se stabilește o conexiune între portul de recepție și portul de destinație asupra căruia sunt transferate datele. Dacă portul de destinație este ocupat, datele pot fi stocate în memoria procesorului portului de intrare. În comutatoarele cu magistrală comună, procesoarele de port sunt conectate printr-o magistrală de mare viteză. Dezavantajul acestor arhitecturi este că nici matricea de comutare, nici magistrala partajată nu permit tamponarea datelor.

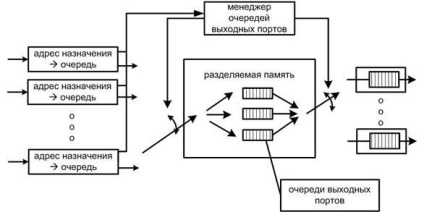

Comutatoarele cu memorie partajată utilizează un bloc de memorie pentru a stoca datele comutate așteptând să calculeze ruta și / sau să elibereze portul de destinație (Figura 1).

Fig. 1. Comutator cu memorie partajată

Blocurile de intrare ale procesoarelor de port sunt conectate la o intrare de memorie partajată comutabilă, iar blocurile de ieșire ale acelorași procesoare sunt conectate la ieșirea comutabilă a acestei memorii. Comutarea între intrarea și ieșirea memoriei partajate este controlată de managerul de coadă al porturilor de ieșire. Acest comutator are o întârziere de transmisie mai lungă, dar pierderea mai mică a datelor. În astfel de comutatoare, procesarea datelor este împărțită în trei acțiuni principale:

· Recepția datelor - procesoarele porturilor de intrare scriu pachetele de date primite în memoria partajată;

Pentru performanța dispozitivului de stocare, această arhitectură are cerințe speciale. Memoria trebuie să furnizeze o lățime de bandă suficientă, astfel încât porturile de intrare să poată accesa memoria pentru scrierea de date fără pierderi; în același timp, porturile de ieșire trebuie să citească datele în timp, astfel încât datele transferate pe mediu să nu întrerupă până la sfârșitul blocului. Adică, capacitatea de memorie este de câteva ori mai mare decât performanța fiecărui canal. Luați în considerare cerințele de memorie pentru un switch Gigabit Ethernet cu 6 porturi. Fiecare port care funcționează în modul full-duplex recepționează simultan și transmite date cu o viteză de 1 Gb / s. Asta înseamnă că memoria trebuie să furnizeze o viteză de transfer de 12 Gb / s.

În astfel de sisteme, se utilizează SRAM static. Această memorie are o interfață mai simplă, deși costul acesteia este mai mare. În cel mai rău caz, 12 porturi de comutare accesează zone de memorie arbitrare pentru scrierea și citirea datelor, ceea ce necesită cicluri suplimentare de activare și închidere a liniilor și a ciclurilor de regenerare. Atunci când se utilizează componente DRAM cu procesare de date prin conducte, întârzierea comutării între șiruri arbitrare este de 2 cicluri cu o lungime a pachetelor de date de 4 cicluri. Cu această operație, memoria dinamică care asigură performanța necesară a comutatorului va necesita o frecvență mai mare de operare în comparație cu memoria statică SRAM.

Plasarea unui bloc de SRAM de memorie cip comutatorul este scump pentru a dezvolta / cumpărare SRAM bloc de memorie de mare viteză, și exigențe ridicate pe producția de cip, în special, necesită o combinație de tehnici de logica obișnuită și stocarea unor volume mari (pentru comutator folosit capacitatea de memorie de 4 MB) . Utilizarea unui cip extern de memorie SRAM poate reduce aceste costuri, dar necesită localizarea elementului pe PCB-ul utilizat în sistem. Cipul de comutare a fost proiectat pentru utilizarea cu un SRAM extern.

Un cip conventional SRAM cu un singur port de citire / scriere pe 32 de biți care rulează la 200 MHz permite trecerea a 6,4 Gbps de date pe secundă, adică asigură funcționarea a 3 porturi. Pentru a crea un comutator cu 6 porturi este necesară pentru a crește capacitatea de memorie de două ori. Pentru a face acest lucru, trebuie să utilizați unul dintre următoarele dispozitive de stocare:

· Memorie pe 32 de biți cu două porturi care funcționează la 200 MHz;

· Memorie pe 64 de biți care rulează la 200 MHz;

· Memorie DDR (rata dublului de date) la 200 MHz;

· Memorie pe 32 de biți cu un singur port care rulează la 400 MHz.

Toate aceste abordări au avantaje și dezavantaje:

· Utilizarea memoriei DPRAM simplifică arbitrul de operare (care funcționează la frecvență înaltă), care acum sunt obligate să monitorizeze și să se ocupe de cererile de jumătate, dar în același timp, crește cantitatea de ieșire semnale de la cip. În acest dual-port de memorie poate fi „adevărat“ dual-port, în cazul în care fiecare memorie de port funcționează la citire și scriere, sau „simplu“ memorie dual-port, atunci când un port este read-only, iar al doilea - numai înregistrările. Pentru un dispozitiv de comutare, cererile de citire și scriere sunt distribuite în mod egal, iar această împărțire a funcționalității porturilor de memorie este nesemnificativă; Pentru alte dispozitive, o astfel de memorie ar trebui selectată ținând cont de cerințele proiectului.

· Selectarea cip de memorie, tactat la 400 MHz, sau utilizarea memoriei DDR sunt asociate cu dificultăți tehnice, deoarece designul necesită nu numai unitatea logică internă capabilă să funcționeze la 400 MHz (care afectează timpul de proiectare și utilizare tehnologie), dar, de asemenea, mai complicat Dezvoltarea unei plăci de circuite imprimate utilizate în sistem. Utilizarea memoriei DDR necesită o mică schimbare în schema de operare a controlerului de acces în memorie.

Abordarea cea mai optimă în raport cu complexitatea dezvoltării / costului este creșterea lățimii magistralei de date. În acest caz, un comutator are un acces pe 64 de biți canal de memorie de citire / scriere, tactat la 200 MHz (pentru un total de 12,8 Gbit / s) și 6 reprezentate prin porturile de comutare utilizând canale de acces 12 de memorie (pentru citire și scriere ). Controlerul de acces la memorie se ocupă de cererile portului de comutare pentru a accesa memoria și oferă un flux de date în timp util și continuu.

Pentru a asigura costuri scăzute de dezvoltare, este necesar ca miezul cipului de comutare să funcționeze la frecvențe mai mici - 50-100 MHz. Astfel de frecvențe sunt realizate cu ajutorul sistemelor CAD cu un efort mult mai mic decât 200-250 MHz, ceea ce implică faptul că dezvoltatorul trebuie să petreacă mult timp sau să utilizeze tehnologii de producție mai scumpe.

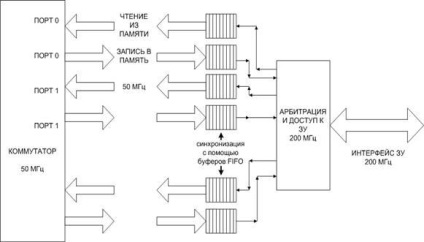

Se propune arhitectura controlerului de interfață de memorie (Figura 2):

· Unitate de interfață de memorie pentru funcționarea la frecvența de acces la memorie mare (200-250 MHz);

· „Intern“ în raport cu interfețele de memorie comutator care funcționează la mediu / frecvența dorită de 50-100 MHz;

· Tampoane de sincronizare și paginare pentru a lega aceste două interfețe.

Memoria cu un singur port SRAM necesită arbitraj între 12 canale de solicitare. Pentru a distribui în mod egal accesul la port în memorie, Schema Round-Robin este cea mai potrivită. Pentru a asigura rata de arbitraj necesară, funcționarea unității poate fi realizată în mai multe cicluri. În același timp, pentru a reduce timpul petrecut pentru accesul la memorie, operațiile de citire / scriere sunt mai avantajoase în modul batch, atunci când un canal citește / scrie mai multe cuvinte secvențial când accesează memoria. În același timp, dimensiunea pachetului nu ar trebui să fie prea mare, astfel încât un canal de scriere sau citire să nu blocheze funcționarea altor porturi. În această lucrare, accesul la memorie a fost efectuat sub formă de pachete de dimensiunea a patru cuvinte pe 64 de biți.

Fig. 2. Schema controlerului de acces la dispozitivul de stocare

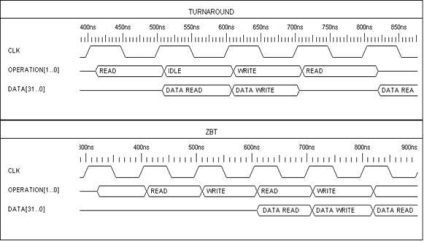

Pentru tehnologii de rețea, care au nevoie de acces de mare viteză de memorie de pe piață sunt componente de memorie ZBT® / Nobl ™ SRAM (Zero Bus Turnaround - ciclu de magistrală de comutare la zero, nici un autobuz Latency - lipsește întârzierea de autobuz). Această memorie asigură transferul maxim al magistralei eliminând ciclul de comutare între operațiile de scriere și citire (Figura 4). Dispozitivele de memorie ZBT® SRAM funcționează atât în flux cât și în tehnologia conductelor. Dispozitivele transportoare funcționează la frecvențe mai înalte, iar dispozitivele de streaming au o întârziere mai mică a datelor.

Majoritatea producătorilor eliberează SRAM cu o magistrală de date crescută, care permite scrierea și citirea biților suplimentari de paritate octet (magistrala de date 18/36 biți). Când se instalează în paralel două cipuri de memorie cu o magistrală de date de 36 biți, cei 8 biți suplimentari disponibili permit utilizarea unor coduri redundante care detectează și corectează erorile. De exemplu, codul Hamming permite erorilor de un bit pe magistrala de date să fie corectate și erorile detectate în două biți. Pentru 32 de biți de date, codul Hamming utilizează 7 biți suplimentari, pentru 64 de biți - 8 biți. Codarea / corectarea erorilor înainte de accesul imediat la memorie permite evitarea creșterii lățimii tampoanelor de sincronizare. Conductarea blocului de arbitrare a cererii de memorie permite, de asemenea, blocarea relativ lentă a codului Hamming de codificare / decodare, care necesită o operație exclusivă OR la 64 de biți din magistrala de date. În acest fel, corectarea erorii este transparentă pentru comutator.

Arhitectura propusă are următoarele proprietăți:

· Două cipuri de memorie instalate în paralel, pentru a asigura lățimea de bandă necesară.

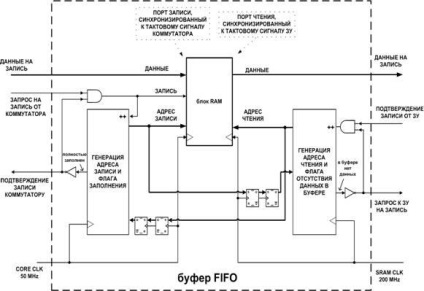

· Sincronizarea datelor din diferite domenii de sincronizare folosind tampoane FIFO.

· Prelucrarea loturilor pentru a reduce timpul de acces / arbitraj.

· Corecția erorilor de un bit / detectarea erorilor în doi biți folosind codul Hamming.

Fig. 3. Tamponul FIFO folosit pentru a scrie date în memorie

Soluția prezentată utilizează performanța maximă a componentei memoriei SRAM. Pentru a dezvolta un comutator cu mai multe porturi sau tehnologia suporta mai rapid (mai rapid decât 1 Gb / s) este necesară pentru a spori și mai mult capacitatea canalului de accese la memorie. În acest caz, abordările utilizate nu pot fi potrivite, iar cea mai probabilă soluție este văzută de a utiliza un tip extern de memorie DDR (II) SDRAM, având o frecvență mai mare de funcționare (pentru limita SRAM este de 300 MHz), sau utilizarea altor tehnologii de fabricație cip pentru a localiza memoria partajată a chip comutator .

Fig. 4. Memorie sincronă cu ciclu de comutare zero în comparație

cu memoria tradițională

În această lucrare se propune arhitectura regulatorului de interfață de memorie, care asigură utilizarea maximă a memoriei SRAM, menținând frecvențele de bază relativ scăzute ale cipului de comutare. Această arhitectură asigură accesul continuu necesar al mai multor canale gigabit ale comutatorului la memorie și permite reducerea costului de utilizare a cipurilor de memorie SRAM și dezvoltarea unei interfețe de acces RF la memorie.

1. Oliforul rețelei. Principii, tehnologii, protocoale. - Sankt-Petersburg. Peter, 20 de ani. il.

2. Standardul ISO 35.100 - Interconectarea sistemelor deschise // www. izo. org.

6. Altera Stratix Device Handbook, Altera Corporation.