Vă mulțumim pentru sprijinul dvs.!

Configurația testului

Numărul de stand 1 (fără un "patch")

Numărul de stand 2 (cu un "patch")

Datele reale / lățimea de bandă a cache-ului de memorie

În primul rând, observăm că testele absolute în acest studiu sunt enumerate AMD Phenom platforma X4 „patch“ pot fi ușor diferite de cele care au fost obținute anterior (fără „plasturi“), din cauza utilizării diferitelor placă de bază (a se vedea. Configurație bancului). În special, la momentul studiului primului sistem (stand №1, placa de baza MSI K9A2 Platinum) nu a fost cunoscut ce fel de Northbridge frecvență și L3-cache a procesorului este setat implicit pe sistem. Pe în articolul de la al doilea sistem (stand №2, placa de baza Gigabyte MA790GX-DQ6) AMD utilitate Overdrive a arătat frecvența controlerului de memorie și procesorul implicit L3-cache setat la 2,0 GHz cu o frecvență de 2,4 GHz nuclee de procesare. Este rezonabil să presupunem că același mod "implicit" este folosit și pe prima placă de bază examinată de noi. În studiul de față, am crescut procesorul de frecvență Northbridge la 2,4 GHz manual, folosind configurația BIOS Setup pentru nuclee de procesor de operare sincronicitate și controler de memorie integrat, și comparând acest mod de operare a procesorului cu un „default“ modul de funcționare (CPU 2,4 GHz, NB 2,0 GHz).

Rezultatele măsurării transferului (PS) al cache-urilor de procesor și RAM sunt prezentate în Tabelul. 1.

Procentaj mediu mediu, octet / ciclu

5,23 GB / s (40,9%)

3,43 GB / s (26,8%)

* Valorile din paranteze sunt relative la limita teoretică a magistralei de memorie FS

După cum s-ar putea aștepta, caracteristicile de viteză ale cache-urilor L1 și L2 ale datelor de bază ale procesorului atunci când se utilizează "patch-ul" nu se modifică. Caracteristicile vitezei L3 cache de mai multe al doilea sistem de creștere (8-11%), în timp ce caracteristicile subsistemului de memorie de mare viteză a redus semnificativ (mai ales în lectura PAC, aproximativ 18%). Deja de la acest test rezultatele pot face o concluzie preliminară că aplicarea „patch-uri“ nu are nici un efect semnificativ asupra procesorului L3-cache (cu creșterile sale PS ca urmare a unei creșteri a ratei de 2.0-2.4 GHz, în timp ce câștigul SS este mai puțin comparativ cu o creștere de 20% a frecvenței), dar afectează lățimea de bandă a memoriei (în ciuda creșterii frecvenței ceasului controlerului de memorie). Validitatea afirmației că nu există nici o influență a "patch-ului" asupra caracteristicilor cache-ului L3 este confirmată de teste suplimentare.

Limitați banda de memorie reală

Caracteristicile limitative ale lățimii de bandă reale a memoriei, prezentate în tabelul. 2, în cazul utilizării "patch" sunt, de asemenea, mai mici: lățimea de bandă maximă citită reală este redusă cu 19,5%, pentru înregistrare - cu aproximativ 4,5%.

18,2 ns

18,6 ns

39,0 ns

225,8 ns

* Dimensiune bloc de 32 MB

Caracteristicile cantitative ale latenței cache-urilor L1, L2 și L3, prezentate în Tabelul. 3, demonstrează o imuabilitate aproape completă atunci când se utilizează "patch-ul", ceea ce confirmă din nou absența efectului "patch-ului" asupra cache-ului L3 al procesorului. O latență a crescut de memorie cantități (aproximativ 13% la accesul pseudo-aleatoare, și mai mult de 2,6 ori (!) Pentru un acces aleatoriu) indică o deteriorare semnificativă a caracteristicilor de viteză ale acestuia din urmă într-o stare de alunecare de nuclee de procesoare L2 D-TLB (adică în Cazul în care aceste erori ar trebui să fie "mascate" de structura "TLB" nedocumentată a controlerului de memorie al procesorului care este dezactivată atunci când se utilizează "patch-ul").

Latența minimă a datelor și memoria cache

Concluziile privind latența medie a datelor și memoria cache pot fi complet extinse la cazul valorilor minime de latență prezentate în Tabelul. 4. Caracteristic remarcat o scădere a eficienței preaducere hardware, manifestată în creșterea latenței memoriei pentru traversal înainte și înapoi, la cerere „patch-uri“, deși acest lucru nu poate fi considerată o consecință directă a dezactiva «TLB» controler de memorie procesor.

Nivel, mod de acces

Latența minimă, ciclurile (ns)

* Dimensiune bloc de 32 MB

** valorile obținute prin metoda nr. 2 în paranteze

Asociativitatea cache-ului de date

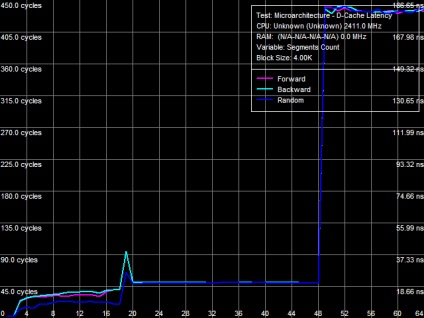

Rezultatul măsurării L1- asociativitate, L2-, și datele L3-cache (Fig. 2) nu are diferențe în ceea ce privește valorile ei înșiși cache asociativ, dar diferă de „alunecare asociativitatea“ toate nivelurile semnificativ mai fine cache, în care se observă atunci când se utilizează mai mult de 48 de segmente de cache. Acest efect este, în mod evident, similar cu lipsa L2 D-TLB, când latențele de acces la memorie trebuie să fie mascate de TLB-ul controlerului de memorie.

Fig. 2. Asocierea cache-ului de date

Lățime de bandă reală a magistralei cache L1-L2

Ca și cache-ul reale real L2, autobuzul real L1-L2 (vezi Tabelul 5) nu se modifică și atunci când se utilizează "patch-ul".

Lățime de bandă reală L1-L2, octet / ciclu

Phenom X4 fără un "patch"

Phenom X4 cu un "patch"

Citirea (direct)

Citirea (inversă)

Înregistrare (direct)

Înregistrare (invers)

Lățime de bandă reală a cache-ului de autobuz L2-L3

În ceea ce privește actualul magistrala PS L2 (core CPU) -L3 (controler de memorie), caracteristicile de performanță (a se vedea. Tabelul 6). Ca măsurat anterior PS L3-cache, pe acest sistem sunt ceva mai mari (aproximativ 8%), în comunicare cu o frecvență mai mare a controlerului de memorie al procesorului (2,4 vs 2,0 GHz).

Lățime reală de bandă L2-L3, octet / ciclu

Phenom X4 fără un "patch"

Phenom X4 cu un "patch"

Citirea (direct)

Citirea (inversă)

Înregistrare (direct)

Înregistrare (invers)

Cache-ul de instrucțiuni, capacitatea efectivă de decodare / executare a codului

Evident, nu există nici un efect al "patch-ului" asupra ratei de decodare / executare a instrucțiunilor din L1-I, precum și a cache-ului L2 al nucleului procesorului (vezi Tabelul 7). În același timp, viteza de execuție a codului din memoria cache L3 crește din nou (aproximativ 8% față de memoria cache L3 PS), datorită creșterii frecvenței acestuia din 2.0 până la 2.4 GHz.

Tip de instrucțiune

(mărime, octet)

Lățime de bandă reală a decodificării / execuției, byte / ciclu (instrucțiuni / ceas)

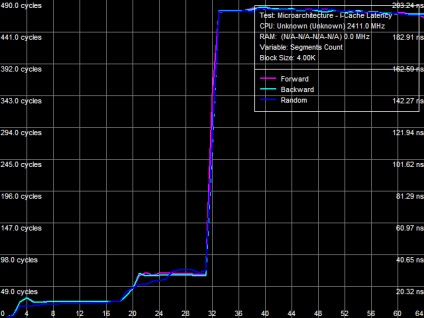

Asociativitatea Instrucțiunii Cache

Testul asociativității cache-ului de instrucțiuni (Figura 3) prezintă o imagine destul de interesantă. Și anume, dispărând ei identificate în seria de teste anterioare (fără „patch-uri“), al doilea asociativitatea inflexiune L3-cache în zona de aproximativ 50 de segmente de cache. În același timp, ca și în testul asociativității cache-ului de date, pedeapsa "eroare asociativă" pentru ultimul nivel al cache-ului procesorului este semnificativ crescută. Prin urmare, se poate concluziona că efectiv asociativ L3-cache cache codul este 14 (32 minus 18), așa cum a observat anterior în a doua îndoire 50 segmente un artefact.

Fig. 3. Asocierea cache-ului de date

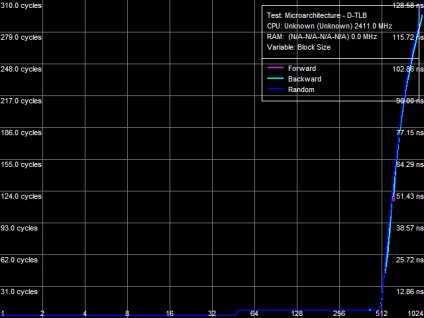

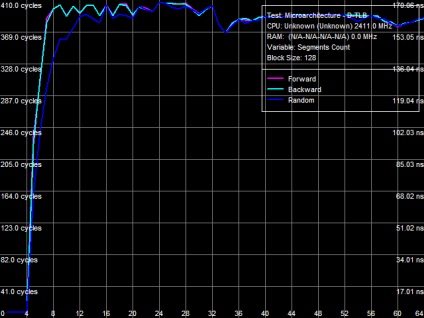

Caracteristici TLB

Așa cum s-ar putea fi de așteptat, cel mai mare efect al includerii „patch-uri“ teste arată procesor TLB. În mod firesc, foarte caracteristicile TLB nu se schimba (deoarece aceste elemente fac parte din arhitectura miezului procesorului), dar crește în mod semnificativ dor de pedeapsă ultimul nivel TLB ca „dimensiune“ și „asociativitatea“.

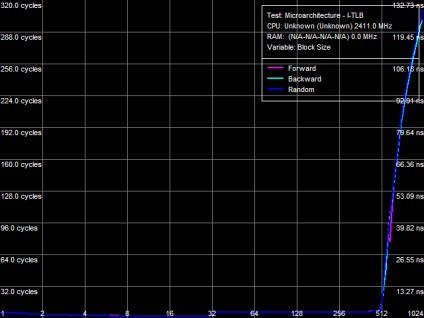

Fig. 4. Dimensiunea D-TLB

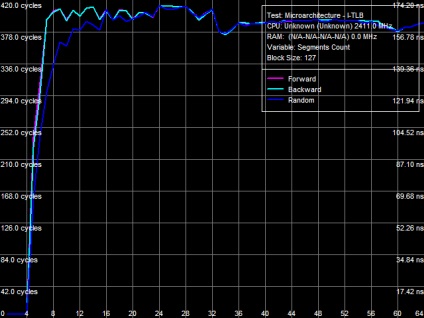

Fig. 5. Asociativitatea L2 D-TLB

În Fig. 4 prezintă rezultatul testului de mărime D-TLB, iar în Fig. 5 - testul asociativității L2 D-TLB. În ambele cazuri, există o creștere semnificativă a pedepsei pierdute L2 D-TLB - aproximativ 290 de cicluri cu epuizarea volumului său și până la 400 de cicluri cu asociativitatea sa epuizată.

Fig. 6. Dimensiunea lui I-TLB

Fig. 7. Asociativitatea L2 I-TLB

Un rezultat similar Testele arată dimensiune (Fig. 6) și asociativitatea (Fig. 7) I-TLB. PIM slip L2 I TLB «size» se ridică la aproximativ 300 de cicluri, și „asociativitatea“ - aproximativ 400 de cicluri, care este aproape de valorile corespunzătoare obținute în testele D-TLB.

Ce concluzii se pot trage din rezultatele cercetărilor efectuate? În primul rând, evident și importantă concluzie este că procesoarele AMD Phenom familia (K10), precum si AMD Athlon 64 (K8) conțin în controler de memorie integrat, o structură care poate fi considerat un tampon de TLB de mare destul de eficiente, atât la manipularea la date (D-TLB) și la executarea codului (I-TLB). Existența acestei structuri în ambele familii de procesoare a demonstrat valori alunecare moderate comanda fine ultimul nivel (L2) D-TLB și I-TLB core localizat în 20-40 de cicluri. În același timp, dezactivați (și este - explicația cea mai rezonabilă a modului în care „patch“ pentru procesoarele AMD Phenom) (! Pana la 300-400 cicluri, adică aproape un ordin de mărime) conduce la o creștere substanțială în cantități considerate alunecare fină . În acest sens, este interesant de menționat și procesoarele "eficiente din punct de vedere energetic" AMD Athlon 64 X2 EE. în care pedeapsa L2 D-TLB și I-TLB este inițial ridicată. Se poate presupune că aceste structuri procesoare „TLB“ controler de memorie găsit sau deloc (ceea ce este puțin probabil, deoarece este imposibil să spunem că este atât de dificil să pună în aplicare și consumă atât de multă energie încât le-a luat destul de exclus din „punct de vedere energetic“ versiuni de procesoare), sau ... este dezactivat inițial din cauza unei erori similare cu eroarea din controlerul de memorie a procesoarelor Phenom (ceea ce este mult mai probabil).

Următoarea concluzie a fi trase din rezultatele studiului nostru constă în faptul că structura «TLB» menționat mai sus se referă în mod specific la memoria controlerului CPU, nu L3-cache (așa cum a fost scris în mesajul de eroare devreme în procesoare Phenom). Acest lucru este confirmat de absența aproape totală a influenței negative a „patch-uri“ la caracteristicile de mare viteză (PS și latență) procesor L3-cache. Astfel, reducerea performanței globale a sistemului atunci când se utilizează „patch-uri“ datorită exclusiv pentru a reduce caracteristicile de viteză ale subsistemului de memorie și, în special, o creștere semnificativă în memorie cu acces aleator latență. Pentru comoditate, le vom prezenta în tabelul rezumativ.

Valoare fără un "patch"

Valoare cu un "patch"

Ideea provoca unele în medie magnitudinea efectului de „patch-uri“ pe o astfel de caracteristici de nivel scăzut bucată cu bucată destul de lipsită de sens - răspândit în valori variind de la 1,7% până la 11,8 ori, și s-au efecte (de exemplu, creșterea amenzilor alunecare TLB) nu se comportă mod la fel de semnificativ în aplicațiile reale datorită "sintetice" excepționale ale caracteristicilor. În același timp, într-un grup comun poate distinge reduce caracteristicile de viteză ale subsistemului de memorie (18-20%), suficient de aproape de realitate, ceea ce este comparabil cu reducerea performanței sistemului în majoritatea aplicațiilor reale care operează pe date mai degrabă „în linie“, mai degrabă decât „aleatoare „mod. În cazul în care accesul aleatoriu la datele pot fi de așteptat pentru a reduce și mai mult performanța generală a sistemului, deoarece accesul de memorie latență în acest mod crește foarte semnificativ.

Dmitry Besedin