Procesoare și jetoane 221

În final, resetarea semnalului MSYN determină resetarea semnalului SSYN și procesul de citire este acum complet.

Un set de astfel de semnale interrelaționate se numește o confirmare completă. Aici, în esență, există 4 evenimente:

1. Setarea semnalului MSYN.

2. Setați semnalul SSYN ca răspuns la semnalul MSYN.

3. Resetați semnalul MSYN ca răspuns la semnalul SSYN.

4. Resetați semnalul SSYN ca răspuns la resetarea semnalului MSYN.

Desigur, interdependența semnalelor nu este sincronă. Fiecare eveniment este declanșat de evenimentul anterior, nu de impulsurile generatorului. Dacă o pereche de dispozitive (master și slave) este lentă, aceasta nu afectează cealaltă pereche de dispozitive, care pot funcționa mult mai repede.

Avantajele unei magistrale asincrone sunt evidente, deși de fapt cele mai multe anvelope sunt sincrone. Ideea este că un sistem sincron este mai ușor de construit decât un sistem asincron. Procesorul central emite pur și simplu semnale, iar memoria le răspunde simplu. Nu există o relație cauză-efect aici, iar dacă componentele sunt selectate cu succes, totul funcționează fără o confirmare. În plus, dezvoltarea pneurilor sincrone a investit o mulțime de resurse.

Până în acest moment, am presupus implicit că există un singur dispozitiv principal al autobuzului - procesorul central. De fapt, chips-urile I / O pot deveni masteri atunci când citesc informații din memorie și scriu informații în memorie. În plus, pot provoca întreruperi. Coprocesoarele pot deveni, de asemenea, dispozitive principale de magistrală. Se pune întrebarea: „Ce se întâmplă atunci când magistrala de conducător auto sunt două sau mai multe dispozitive în același timp?“ Pentru a evita haosul care poate avea loc în același timp, avem nevoie de un mecanism special - așa-numitul arbitraj autobuz.

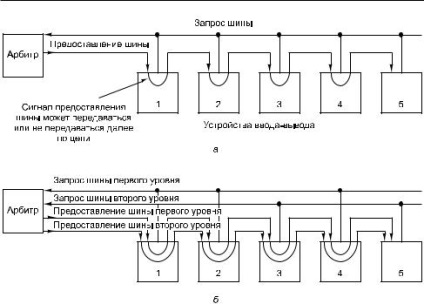

Arbitrajul poate fi centralizat sau descentralizat. Gândiți-vă mai întâi la arbitrajul centralizat. Un exemplu simplu de arbitraj centralizat este prezentat în Fig. 3.37, a. În acest exemplu, un arbitru de magistrală determină ce coadă va fi următoarea. De multe ori, mecanismul de arbitraj este integrat în chip-ul procesorului, dar uneori se utilizează un cip separat. Autobuzul conține o linie de solicitare (OR), care poate fi inițiată de unul sau mai multe dispozitive în orice moment. Arbitrul nu poate determina câte dispozitive solicită autobuzul. El poate determina numai prezența sau absența cererilor.

Atunci când arbitrul detectează o cerere de magistrală, stabilește o linie de alocare a magistralei. Această linie conectează secvențial toate dispozitivele de intrare-ieșire (ca într-o ghirlandă de pom de Crăciun). Când dispozitivul cel mai apropiat de arbitru primește un semnal de acordare a magistralei, acest dispozitiv verifică dacă există o solicitare a magistralei. Dacă există o solicitare, dispozitivul utilizează magistrala, dar nu distribuie semnalul de acordare mai departe de-a lungul liniei. Dacă nu există nicio solicitare, dispozitivul trimite un semnal de acord pe magistrală către următorul dispozitiv. Acest dispozitiv este, de asemenea,

Capitolul 3. Nivelul logic digital

Fig. 3,37. Arbitraj cu autobuz centralizat pe un nivel cu interogare consecutivă (a); arbitraj centralizat pe două niveluri (b)

are încredere dacă există o cerere și acționează în consecință, în funcție de prezența sau absența cererii. Transmisia acordării autobuzului este continuată până când un dispozitiv beneficiază de autobuzul furnizat. Un astfel de sistem este numit sistem secvențial de votare. În acest caz, prioritățile dispozitivelor depind de cât de apropiate sunt arbitrul. Aparatul cel mai apropiat de arbitru are cea mai mare prioritate.

Pentru ca prioritățile dispozitivelor să fie independente de distanța de la arbitru, unele niveluri suportă mai multe nivele de prioritate. La fiecare nivel de prioritate există o linie de solicitare a magistralei și o linie de acordare a magistralei. În Fig. 3.37, b arată 2 niveluri (deși în realitate autobuzele suportă de obicei 4, 8 sau 16 nivele). Fiecare dispozitiv este asociat cu unul dintre nivelurile de solicitare a magistralei, iar cu cât este mai mare nivelul de prioritate, cu atât mai multe dispozitive sunt legate de acest nivel. În Fig. 3.37, b puteți vedea că dispozitivele 1, 2 și 4 au nivelul de prioritate 1 și dispozitivele 3 și 5 - nivelul de prioritate 2.

Dacă se solicită mai mult de un nivel de prioritate în același timp, arbitrul oferă busului cel mai înalt nivel. Printre dispozitivele cu aceeași prioritate este implementat un sistem secvențial de votare. În Fig. 3.37, b că în cazul dispozitivului de conflict 2 „câștigă“ dispozitivul 4 și dispozitivul 4 „câștigă“ dispozitivul 3. Dispozitivul 5 are cea mai mică prioritate, deoarece este situat la capătul cel mai scăzut nivel.

Trebuie remarcat faptul că, din punct de vedere tehnic, linia de furnizare a autobuzelor Layer 2 nu trebuie să lege în mod secvențial dispozitivele 1 și 2, deoarece nu pot trimite solicitări către aceasta. Cu toate acestea, mult mai ușor

Chips-uri de procesor și bus 223

conduce toate liniile de furnizare a autobuzului prin toate dispozitivele decât să conecteze dispozitivele într-un mod special, în funcție de prioritățile lor.

Unii arbitri conțin oa treia linie, care este setată de îndată ce dispozitivul primește semnalul de acordare a magistralei și primește autobuzul la dispoziția sa. Odată ce această linie de confirmare este stabilită, liniile de solicitare și de acordare pot fi resetate. Ca rezultat, alte dispozitive pot solicita o magistrală în timp ce primul dispozitiv o folosește. Până când se termină transmisia curentă, va fi deja selectat următorul master. Acest dispozitiv poate porni funcționarea imediat ce linia de confirmare este resetată. Din acest moment, începe următorul ciclu de arbitraj. Această structură necesită o linie suplimentară și mai multe circuite logice în fiecare dispozitiv, dar, în același timp, ciclurile de autobuz sunt folosite mai rațional.

În sistemele în care memoria este conectată la magistrala principală, procesorul trebuie să concureze cu toate dispozitivele I / O la aproape fiecare ciclu al magistralei. Pentru a rezolva această problemă, puteți oferi CPU cea mai mică prioritate. În acest caz, magistrala va fi furnizată procesorului numai dacă nu este necesară de nici un alt dispozitiv. CPU-ul poate aștepta mereu, iar dispozitivele I / O trebuie să acceseze magistrala cât mai repede posibil, astfel încât să nu piardă date. De exemplu, discurile care se rotesc la viteză mare nu pot aștepta. În multe computere moderne, pentru a rezolva această problemă, memoria este plasată pe un autobuz, iar dispozitivele I / O pe de altă parte, deci nu trebuie să se oprească pentru a acorda acces la autobuz.

De asemenea, este posibil arbitrajul autobuzului descentralizat. De exemplu, un computer poate conține 16 linii prioritare de comandă a magistralei. Când un dispozitiv are nevoie de o magistrală, acesta își stabilește propria linie de solicitare. Toate dispozitivele monitorizează toate liniile de solicitare, astfel încât, la sfârșitul fiecărui ciclu de autobuz, fiecare dispozitiv poate determina dacă are în prezent cea mai mare prioritate și, prin urmare, este permis să utilizeze magistrala în următorul ciclu. Această metodă necesită mai multe linii, dar elimină costul potențial al resurselor pentru utilizarea arbitrului. În acest caz, numărul de dispozitive este limitat de numărul de linii de solicitare.

Cu un alt tip de arbitraj descentralizat, se folosesc doar trei linii, indiferent de câte dispozitive sunt disponibile (Figura 3.38). Prima linie este montajul OR. Este necesar pentru o cerere de magistrală. A doua linie se numește BUSY și înseamnă ocuparea forței de muncă. Se pornește de către maestrul magistralei curente. A treia linie servește pentru arbitrarea autobuzului. ea

Fig. 3.38. Decizia autobuzelor descentralizate

Capitolul 3. Nivelul logic digital

conectă secvențial toate dispozitivele. Începutul circuitului este conectat la o sursă de alimentare cu o tensiune de 5 V.

Dacă nu este necesară nici o magistrală pentru niciunul dintre dispozitive, linia de arbitraj transmite semnalul către toate dispozitivele. Pentru a avea acces la magistrala, dispozitivul verifică mai întâi dacă busul este liber și dacă semnalul arbitral IN este setat. Dacă semnalul IN nu este setat, dispozitivul nu poate deveni magistrala magistralei.

În acest caz, se resetează semnalul OUT. Dacă semnalul IN este setat, dispozitivul resetează de asemenea semnalul OUT, în urma căruia următorul dispozitiv nu primește semnalul IN și, la rândul său, resetează semnalul OUT. În consecință, toate dispozitivele care urmează circuitului nu primesc semnalul IN și resetați semnalul OUT.

Ca urmare, rămâne un singur dispozitiv în care semnalul IN este setat și semnalul OUT este resetat. Acesta devine masterul magistralei, stabilește linia BUSY și semnalul OUT și apoi pornește transferul de date.

După un mic gând, puteți afla că din toate dispozitivele care au nevoie de un autobuz, bara de bare devine cea mai stângă. Un astfel de sistem seamănă cu un sistem secvențial de vot, numai în acest caz nu există arbitru, deci costă mai puțin și funcționează mai repede. În plus, nu există probleme cu eșecurile arbitrilor.

Principiile funcționării autobuzelor

Până în acest moment, am discutat numai cicluri normale de autobuz, atunci când comandantul (de obicei procesorul central) citește informații de la sclav (de obicei din memorie) sau scrie informații la acesta. Cu toate acestea, există mai multe tipuri de cicluri de autobuz. Să ne uităm la unele dintre ele.

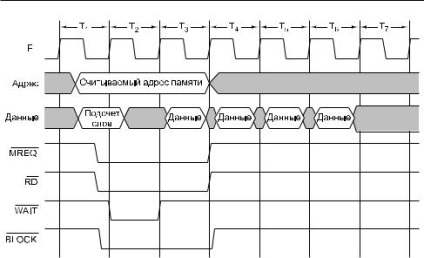

De obicei, un cuvânt este transmis la un moment dat. Când utilizați cache-ul, este de dorit să apelați imediat întreaga linie de cache (adică 16 cuvinte consecutive de 64 de biți). Cu toate acestea, de multe ori blocarea transferului poate fi mai eficientă decât o astfel de transmitere serială a informațiilor. Când blocul începe să citească, comandantul îi spune slavei câte cuvinte să trimită (de exemplu, punând numărul total de cuvinte pe liniile de informare în perioada T 1). În loc să emită un cuvânt ca răspuns, comandantul emite un cuvânt pentru fiecare ciclu până când se transmite numărul necesar de cuvinte. În Fig. Figura 3.39 prezintă aceeași schemă ca în Fig. 3.35, numai cu un semnal suplimentar BLOCK, care indică faptul că blocul este solicitat. În acest exemplu, citirea unui bloc de patru cuvinte durează 6 cicluri în loc de 12.

Există și alte tipuri de cicluri de anvelope. De exemplu, dacă vorbim despre sisteme cu două sau mai multe procesoare centrale pe aceeași magistrală, trebuie să fii sigur că la un moment dat un singur procesor central poate folosi o anumită structură de date în memorie. Pentru a ordona acest proces, memoria trebuie să conțină o variabilă care ia valoarea 0 atunci când procesorul central utilizează structura de date și 1 atunci când structura de date nu este utilizată. Dacă CPU trebuie să acceseze structura de date, trebuie să citească variabila, iar dacă este 0, o dă o valoare de 1. Problema este că cele două

Chips-uri de procesor și bus 225

Fig. 3.39. Transferul blocului de date

Procesoarele centrale pot citi o variabilă pe ciclurile de autobuz consecutive. Dacă fiecare procesor detectează că variabila este 0 și apoi modifică valoarea variabilei la 1, ca și cum ar folosi doar această structură de date, atunci o astfel de secvență de evenimente va duce la haos.

Pentru a preveni o astfel de situație, sistemele multiprocesoare au un ciclu special de autobuz care permite oricărui procesor să citească un cuvânt din memorie, să îl verifice și să îl schimbe și apoi să îl scrie în memorie; întregul proces are loc fără eliberarea anvelopei. Un astfel de ciclu nu permite altor procesoare centrale să utilizeze magistrala și, prin urmare, să interfereze cu funcționarea primului procesor.

Un alt ciclu important al autobuzului este ciclul de întrerupere a serviciului. Când procesorul instruiește dispozitivul I / O să facă ceva, așteaptă o întrerupere după oprire. Un semnal de întrerupere necesită o magistrală.

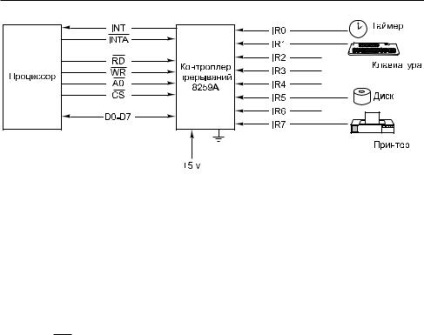

Deoarece poate exista o situație în care mai multe dispozitive simultan vor să efectueze o întrerupere, există aceleași probleme de rezolvare a conflictelor ca în ciclurile de autobuz convenționale. Pentru a evita astfel de probleme, este necesar ca fiecare dispozitiv să atribuie o anumită prioritate și să sprijine arbitrajul centralizat pentru distribuirea priorităților. În aceste scopuri, există o interfață de întrerupere standard utilizată pe scară largă. În computerele IBM PC și modelele ulterioare pentru aceasta este chip Intel 8259A. Este arătat în Fig. 3,40.

Până la opt controlere I / O pot fi conectate direct la opt intrări IR x (Interrupt Request) ale cipului 8259A. Când unul dintre aceste dispozitive decide să întrerupă, acesta pornește linia de intrare. Când una sau mai multe intrări sunt activate, controlerul 8259A emite o intrare INT (INTerruptă)

Capitolul 3. Nivelul logic digital

Fig. 3,40. Întrerupător de comandă 8259A

8259A conține mai multe registre pe care CPU le poate citi și scrie utilizând cicluri comune de autobuz și RD (ReaD read), WR (WRite), CS (Chip Select) și A0. Când software-ul a procesat întreruperea și este gata să primească următoarea, scrie codul special la unul dintre registre, ceea ce determină resetarea INT prin cipul 8259A, dacă nu se produce o altă întrerupere. De asemenea, registrele pot fi scrise pentru a transforma 8259A într-unul din mai multe moduri și pentru a efectua alte funcții.

Cu mai mult de 8 dispozitive I / O, chips-urile 8259A pot fi cascadate. În situația cea mai extremă, toate cele 8 intrări pot fi conectate la ieșirile altor 8 8259A, conectând până la 64 de dispozitive I / O la un sistem de service în două etape de întrerupere. Controlerul I / O I / O Intel ICH10, unul dintre chipset-urile chipset-ului Core i7, conține două controlere de întrerupere 8259A. Astfel, ICH10 are 15 întreruperi externe - 1 mai puțin de 16 întreruperi ale doi controlori 8259A, deoarece una dintre întreruperi este utilizată pentru cascadarea celui de-al doilea controler 8259A. Cipul 8259A conține mai mulți pini pentru o conexiune în cascadă, dar le-am scăpat pentru simplitate. Astăzi, modelul 8259A face parte dintr-un alt cip.

Deși descrierea de mai sus nu epuizează toate aspectele de dezvoltare a pneurilor, oferă suficiente informații pentru o înțelegere generală a principiilor anvelopei și principiile de interacțiune cu autobuzul CPU. Acum trecem de la general la specific și luăm în considerare câteva exemple concrete de procesoare și autobuze.