Organizarea accesului direct la memorie

Controler de acces direct pentru memorie KR580IK57 (KR580VT57)

Secvența programării controlerului

Organizarea accesului direct la memorie

O modalitate de a face schimb de date cu UV se schimbă în modul de acces direct la memorie (DMA). În acest mod, schimbul de date între UV și memoria principală a microcomputerelor are loc fără participarea procesorului. Schimbul în modul DMA este controlat nu de programul executat de procesor, ci de circuitele electronice externe procesorului. În mod obișnuit, schemele care controlează schimbul în modul DMA sunt plasate într-un controler special, numit un controler direct de acces la memorie.

Schimbul de date în modul DMA permite utilizarea de dispozitive de stocare de mare viteză microcomputer externe, cum ar fi hard disk-uri, disc magnetic, deoarece PDP poate oferi un timp de partajare cu un octet de date între memorie și HEV ciclu de acces de memorie egal.

Există două tipuri de acces direct la memorie, cu "captură de buclă". Cea mai simplă modalitate de a organiza un DMA este de a folosi acele cicluri de CPU pentru schimbul în care nu schimbă date cu memorie. În astfel de cicluri, controlerul DMA poate schimba datele cu memoria, fără a interfera cu funcționarea procesorului. Cu toate acestea, este necesar să se izoleze astfel de cicluri, astfel încât să nu existe o suprapunere temporară în schimbul PDR cu operațiunile de schimb inițiate de procesator. La unele procesoare, se generează un semnal special de control, indicând ciclurile în care procesorul nu accesează interfața sistemului. Atunci când se utilizează alte procesoare pentru a izola astfel de cicluri, este necesar să se utilizeze circuite selective speciale în controlerele PDP, ceea ce le complică designul. Aplicarea metodei considerate de organizare a PDP nu reduce performanța microcalculatorului, dar în acest caz schimbul în modul DMA este posibil numai în momente aleatorii prin octeți sau cuvinte.

Mai frecvent este RAP cu "ciclul de captură" și deconectarea forțată a procesorului de la magistrala de interfață a sistemului. Pentru a pune în aplicare un astfel de regim DMA sistem de interfață microcalculator este completată de două linii pentru transmiterea semnalelor de control „cerință pentru accesul direct la memorie“ (TPDP) și „Furnizarea de acces direct la memorie“ (CNDO).

Semnalul de comandă al TPR este format din controlerul de acces direct al memoriei. Procesorul, după primirea acestui semnal, suspendă executarea următoarei comenzi, fără a aștepta finalizarea acestuia, emite interfeței sistemului semnalul de comandă al APDU și se deconectează de la autobuzele interfeței sistemului. Din acest punct, toate autobuzele interfeței sistemului sunt controlate de controlerul PDP. Controlerul DMA, utilizând interfața de sistem, schimbă un cuvânt cu un octet sau un cuvânt de date cu memoria microcomputerelor și apoi, înlăturând semnalul TTP, readuce controlul interfeței sistemului la procesor. Odată ce controlerul DMA este gata să schimbe următorul byte, acesta din nou "captează" ciclul procesorului etc. În intervalele dintre semnalele TTP, procesorul continuă să execute instrucțiunile programului. Astfel, executarea programului încetinește, dar într-o măsură mai mică decât atunci când se schimbă în modul de întrerupere.

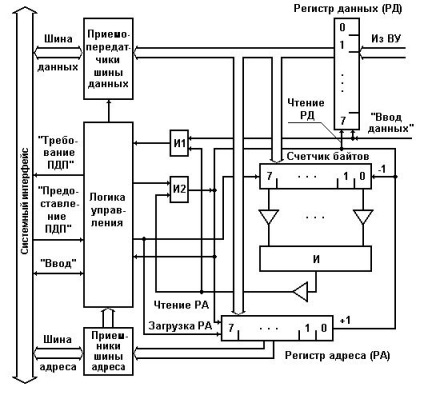

O diagramă bloc a unui controler simplu PDP care oferă date de intrare în memoria unui microcalculator la inițiativa UM în modul "Ciclu de captare" este prezentată în Fig. 1.

Fig. 1. Controlorul DMA pentru introducerea datelor din UV în modul "ciclu de captare" și deconectarea procesorului de la magistrala de interfață a sistemului

Folosind exemplul unui controler DMA simplu, am considerat doar procesul de pregătire a controlerului și transferul direct al datelor în modul DMA. În practică, orice sesiune de schimb de date cu UV în modul DAP este întotdeauna inițiată de programul executat de procesor și include următorii doi pași.

1. În pregătirea pentru următoarea sesiune UV modul procesor de schimb, schimb controlat de programul interoghează starea TDM (verifică disponibilitatea sa de a împărtăși), și trimite o echipa de UW instruirea la schimbul de sclavi. O astfel de pregătire poate fi redusă, de exemplu, pentru a muta capetele pe piesa dorită în hard disk-ul de pe hard disk. Apoi, registrele controlerului DMA sunt încărcate. Aceasta se pregătește pentru schimbul în modul DMA, iar procesorul trece la alt program.

2. Schimbul de date în modul RAP începe după finalizarea operațiunilor pregătitoare în UV, la inițiativa fie a UV, după cum sa discutat mai sus, fie a procesorului. În acest caz, controlerul PDP trebuie completat cu un registru de stare și control, al cărui conținut determină modul de operare al controlerului PDP. Unul dintre biții din acest registru va iniția schimbul de date cu UV. Încărcarea informațiilor în registrul stării și controlului controlerului PDP se face programabil.

Cel mai frecvent este schimbul în modul de acces direct la memorie cu blocarea procesorului. Aceasta diferă de DAP cu "captură de buclă" prin aceea că controlul interfeței de sistem este transferat la controlerul DMA nu pentru timpul de schimb cu un octet, ci pentru timpul de schimb de blocuri de date. Un astfel de mod DMA este utilizat în cazurile în care timpul de schimb al unui octet de la UV este comparabil cu ciclul busului de sistem.

Într-un microcomputer, se pot utiliza mai multe vehicule montate pe vehicul în modul DMA. Furnizarea unei astfel de interfețe de sistem pentru magistrale de magistrală pentru schimbul de date se realizează pe o bază prioritară. Prioritățile slave puse în aplicare în același mod ca și în schimbul de date în modul de întrerupere, dar în loc de semnalele de control „întrerupe cerință“ și „întrerupe redare“ semnalele sunt utilizate „cerință pentru acces direct“ și „Furnizarea de acces direct“, respectiv.

Controler de acces direct pentru memorie KR580IK57 (KR580VT57)

Procesorul gestionează schimbul de date în computer cu construcția sa clasică. Totuși, o astfel de sarcină precum schimbul de date cu dispozitive periferice (adică atunci când se comunică cu lumea exterioară) este încercată, dacă este posibil, prin intermediul dispozitivelor specializate de schimb de informații. Aceasta permite, pe de o parte, eliberarea procesorului (și, în același timp, a programatorului) de îndeplinirea acestei sarcini, pe de altă parte, pentru a face schimbul de date necesar cu o viteză mai mare decât procesorul ar putea face. La urma urmei, perifericele sunt capabile să funcționeze la o viteză comparabilă cu viteza procesorului. Astfel de dispozitive includ, de exemplu, un controler de afișaj sau unități pe discuri magnetice flexibile sau dure. Toate acestea necesită prezența unui așa-numit controler de acces direct al memoriei în sistem, care permite înlocuirea procesorului și organizarea unui schimb de date mai rapid și mai direct între memorie și dispozitivul periferic specificat.

Utilizarea BIS DSP permite reducerea semnificativă a costurilor hardware în implementarea accesului direct la memorie.

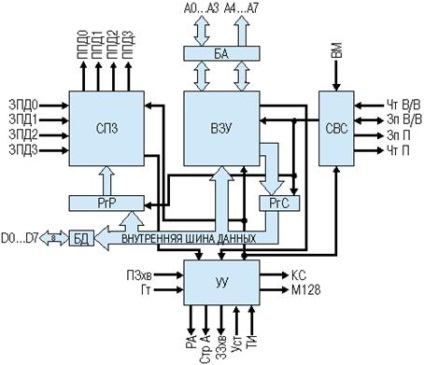

În Fig. 2 prezintă schema structurală a KR580IK57, în Tabelul. 1-pin atribuire.

Fig. 2. Structura microcircuitului KR580IK57

Tabelul 1. Asignarea pinului

Schema de primire a cererilor SDR este destinată recepționării și legării semnalelor nesincronizate pentru cererile de organizare a accesului direct la memorie de la patru dispozitive, precum și emiterea de semnale de confirmare. Fiecare dintre cele patru canale este legat de LSI BDP prin linii separate de solicitări și prin confirmarea accesului direct. Emiterea unui răspuns de confirmare pentru canalul corespunzător are loc în funcție de prioritatea sa.

Secvența de operațiuni în timpul ciclurilor de buclă de control este controlată de unitatea de control a unității de control.

Circuitul de generare a semnalelor SHS efectuează recepția, generarea și emiterea de semnale care asigură schimbul de informații între procesor și microcircuit - pe de o parte și dispozitivele de memorie și periferice - pe de altă parte.

RGR Modul de instalare stochează registrul de informații despre modurile de operare BIS, care includ „Startup“, „End-stop cont“, „intrare extinsă“, „Normal Recording“, „prioritate Rotire“ și „prioritate fixă“.

PrP se încarcă în mod normal după setarea PrA și Pr2 și se resetează prin setarea semnalului Set.

Descărcări 0. 3 PrP permit funcționarea canalului corespunzător. Descărcări 4. 7 furnizați modul de funcționare corespunzător al LSI. Deci, când înregistrați "1" în biți 4Pgr, prioritatea fiecărui canal se modifică.

Canalul difuzat va avea cea mai mică prioritate. Ordinea întreținerii canalului este stabilită în conformitate cu numerele lor 0 >> 1> 2> 3> 0. Dacă bitul 4 PrP este setat la "0", fiecare canal va avea o prioritate fixă. Deci, canalul 0 are cea mai mare prioritate, iar canalul 3 - cea mai mică prioritate. Atunci când "1" este scris în al 5-lea PrP, modul "Extended recording" este setat. În acest mod, durata semnalelor ZpP și Zn V / V crește atunci când nu există semnal de pregătire al dispozitivului extern. În acest caz, LSI intră în starea de așteptare.

Atunci când "1" este scris la al 6-lea PrP, este setat modul "End of account - stop". În acest caz, după apariția semnalului CS, canalul servit va fi interzis. Dacă este necesar să continuați serviciul acestui canal, bitul de rezoluție este reprogramat. La "0" în banda Prg, apariția semnalului CS nu interzice reparația repetată a canalului.

La "1" din categoria 7 PrP setați modul "Startup", permițând canalului 2 să reseteze matricea de date sau să lege un număr de rețele fără intervenția software-ului.

Registre canal 3 stochează informații pentru a reseta registrul canalului 2. După transmiterea KS semnal de bloc și apariția conținutului registrului canalului 3 este transferat în registre canalul corespunzător 2. De fiecare dată când înregistrează în canalul 2 se înregistra informații o „substituție“ canal de date 3, Este setat bitul "Bara de actualizare a datelor" din registrul de stare al canalului.

Registrul de stare al canalului PgC indică numărul canalului care a ajuns la sfârșitul contorului. În plus, PrgS include bitul "Actualizare date de pavilion" descris mai sus.

În procesul de funcționare ca parte a sistemului microprocesor, microcircuitul poate fi în una din următoarele stări: inițială, programare, așteptare, service.

În starea inițială, cipul traduce semnalul extern Set. În această stare, toate cererile pentru canalele AP sunt mascate și tampoanele A0. A3 sunt transferate la starea de primire a informațiilor. În starea de programare, MP are acces la registrele interne ale canalului selectat, în conformitate cu Tabelul. 2 și 3.

În starea de așteptare, microcircuitul este fie de la sfârșitul programării până la ieșirea semnalului PDP, fie între ciclurile TD.

După primirea de la semnalul MF PZhv în prezența unui semnal de cerere, cipul generează semnalul PAP și trece la starea de întreținere în care busurile sistemului sunt controlate de BIS RAP.

A3 A2 A1 A0 Registrul de operare

0 0 0 1 Зп Canal 0, număr de cicluri

0 0 1 1 Зп Canalul 1, numărul de cicluri

0 1 0 1 Зп Canalul 2, numărul de cicluri

0 1 1 1 3 Canalul 3, numărul de cicluri

1 0 0 0 Th Citiți PgC

1 0 0 0 3n Înregistrarea în Prp

Secvența programării controlerului

Pentru început, trebuie să programați PrA și Pr2 ale canalului selectat (sau canalele selectate).

Asta e tot. Acum, controlerul DMA trimite ciclic spațiul de memorie 76D0H-7FF3H la controlerul de afișaj, suspendând procesorul pentru acest timp.

Toate materialele din secțiunea "Informatică"