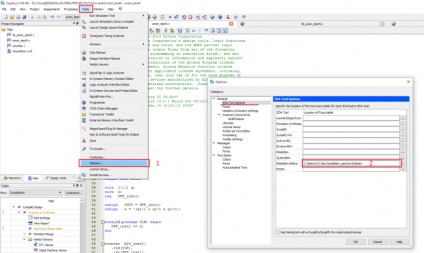

Primul pas este să vă asigurați că calea către instrumentul ModelSim este specificată în mediul de dezvoltare Quartus II. Pentru aceasta, deschideți meniul Instrumente -> Opțiuni. În opțiuni, mergeți la opțiunea Generale -> Instrumentul EDA. Găsiți câmpul ModelSim-Altera și tastați C: \ altera \ 13.0sp1 \ modelsim_ase \ win32aloem sau apăsați butonul cu trei puncte, căutăm acest director pe computer. Firește, pentru versiunea Quartus, diferită de cea a mea, veți avea calea dvs. spre directorul "win32aloem".

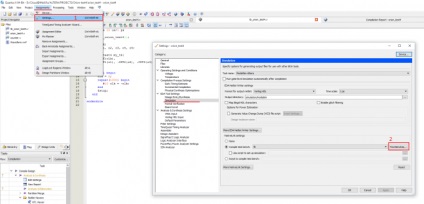

Aveți un proiect pentru FPGA în Quartus II. Cum se scrie teste, sau testbenchi (testbench) - acesta este un subiect pentru un articol separat. Acum presupuneți că testbench-ul dvs. este deja scris. Acum trebuie să spuneți mediul de dezvoltare care test pe care doriți să-l utilizați când simulați. Pentru a face acest lucru, deschideți setările prin meniul Assignments -> Settings. În fereastra care se deschide, în cadrul EDA Tool Settings -> Simulation. apasam pe butonul Test Benchs. Apoi, apropo, puteți seta mai multe teste și când compilați proiectul, treceți la cel dorit.

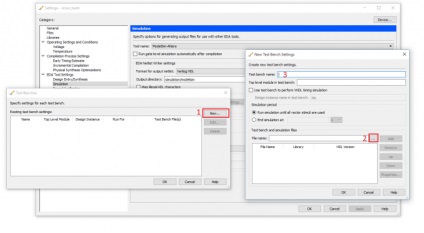

Fereastra de testare pentru banda de test a fost deschisă. Până acum nu am creat niciun testbench, așa că lista este goală. Faceți clic pe butonul Nou. În fereastra Setări pentru noul test Bench care se deschide, trebuie să setați setările de testare.

În partea stângă a câmpului Nume fișier, faceți clic pe butonul cu trei puncte. Selectați fișierul cu codul testbench și faceți clic pe Deschidere. Faceți clic pe butonul Adăugați. Testul a apărut pe lista de testări.

După aceea, în modulul de nivel superior de pe bancul de testare, să specificăm numele modulului de nivel superior care este definit în testbench. Numele din câmpul Nume banda de test poate fi introdus în orice, în mod implicit va fi creat automat același nume ca și numele modulului.

Totul, setăm setările de test de bază. Apăsați OK de două ori. Testul nostru a apărut în lista drop-down a băncilor de test. Încă o dată, faceți clic pe OK.

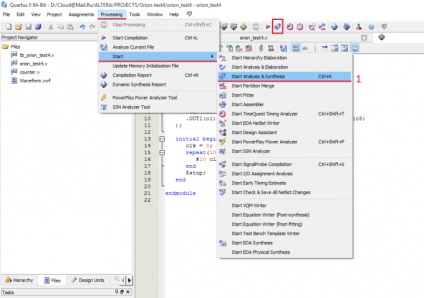

Dacă nu ați făcut deja sinteza proiectului, atunci este timpul să faceți acest lucru. Selectați din meniul Procesare -> Start -> Start Analiză Sinteza. sau apăsați Ctrl + K. sau faceți clic pur și simplu pe pictograma corespunzătoare din panoul superior.

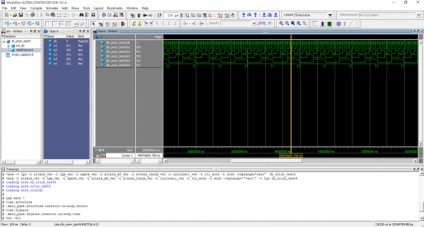

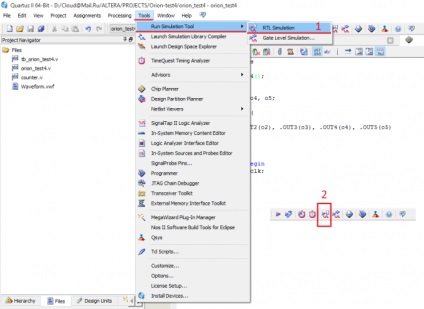

Puteți rula simularea. Selectați Instrumente -> Instrument Simulare Executare -> Simulare RTL (1) sau faceți clic pe simbolul RTL din panoul superior (2).

Instrumentul ModelSim este lansat. care va executa toate instructiunile prescrise in testbench si se va opri (daca ati specificat acest lucru cu directiva $ stop in codul de test). Ecranul va afișa nivelurile semnalelor de intrare și ieșire ale FPGA pe care le-ați descris în proiect.