Cererile de procesare pentru procesor se încadrează într-un set de logică sistem (numit și un chipset), incluzând, printre altele, un controler de memorie. Controlerul de memorie este complet transparent pentru programator, dar cunoașterea caracteristicilor sale arhitecturale facilitează foarte mult optimizarea schimbului de memorie.

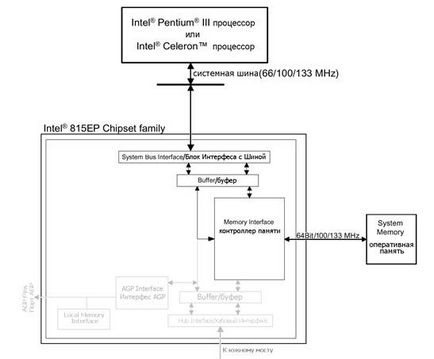

Dispozitivul din podul nord al chipset-ului Intel 815EP, care conține (printre altele) un controler de memorie

Controlerul de autobuz (BIU - Bus Interface Inițializare), „implantate“ în Northbridge chipseta͵ primirea cererii de procesor, în funcție de situația sau trimite-l la agentul corespunzător (în cazul nostru - controler de memorie RAM pas) sau pune cererea într-o coadă în cazul în care agentul în acest moment este ocupat cu ceva. Necesitatea unei cozi din cauza faptului că procesorul poate trimite următoarea cerere, fără a aștepta finalizarea procesării celui anterior, și dacă da, întrebările trebuie să fie depozitate undeva.

Având în vedere dependența controlerului de memorie otarhitektury funcționează cu memorie, sau numai viteza bus de sistem (controler sincron) sau sub-memorie Hered orice altă frecvență (controler asincron). Controlorii sincronici limitează PC-urile utilizatorilor la alegerea modulelor de memorie, dar, pe de altă parte, controlerele asincrone sunt mai puțin productive. De ce? În primul rând, din cauza discrepanță de frecvență, citește datele nu sunt transmise direct la controlerul de autobuz, și Com-ditsya ori mai întâi în tamponul intermediar, în cazul în care controlerul de autobuz va fi capabil de a le regăsi cu el viteza dorită. (O similară situa-TION se observă cu intrarea.) În al doilea rând, în cazul în care frecvența de autobuz de sistem și ceasul de memorie nu sunt legate ca numere întregi, înainte de schimb trebuie să aștepte finalizarea impulsului de ceas curent. Există două astfel de întârzieri (în limbajul comun al unei pedepse):

la transmiterea datelor citite către controlerul de bord.

Toate acestea cresc în mod semnificativ latența subsistemului de memorie - adică timpul dintre trimiterea cererii și primirea datelor. Τᴀᴋᴎᴍ ᴏϬᴩᴀᴈᴏᴍ, controler asincron care funcționează cu un sistem de bus SDRAM PC-133 în memorie ?? e 100 MHz, își pierde colegul său sincron, care rulează pe aceeași anvelopă ?? e cu SDRAM PC-100 de memorie.

Controlorul de magistrală, după ce a primit o notificare din partea controlorului de memorie că datele solicitate sunt pregătite, așteaptă eliberarea magistralei și o trimite la procesor în modul lot. Având în vedere dependența tipului de autobuz pe un ciclu, pot fi transmise una până la patru porțiuni de date. Astfel, în procesele KB, RI și R-SH, se efectuează o transmisie per ceas, în procesorul Athlon sunt două, iar în procesorul P-4 patru.

De acum înainte, datele sunt stocate în cache și sunt disponibile pentru procesor.

Sistem bus controler responsabil pentru interogări de prelucrare și a datelor strămutate-schenie între procesor și chipset-ul, este alcătuit din următoarele componente funcționale: un transfer de date (Procesor Sursa Synch Ceas Transceiver), cere planificator (Command Queue - CQ), cerere Controleri-ra cozi (Control System Queue - CSQ) și agentul de tranzacții (XCA). Componentele rămase ale controlerului de magistrală prezente în Fig. 2.11, sunt necesare pentru a sprijini depanarea sondei, care nu este relevantă pentru subiectul în discuție și, prin urmare, nu este luată în considerare aici.

Transferul de date - într-un sens mai înalt, este un controler de bus "gol", care înțelege protocolul de magistrală și are grijă de toată comunicarea cu procesorul. Solicitările primite de la procesor sunt transferate către programatorul cererilor, de unde sunt trimise agenților corespunzători în momentul în care sunt eliberați.

Agenți Răspunsurile sunt stocate în trei cozi separate: citește coadă (SysDC Citire Coadă - SRQ), memorie coadă de scriere (Memorie Scriere Coadă - MWQ) și PCI intrări coadă bus (PCI / A-PCI Write Queue - AWQ). Notă: în acest caz este vorba despre scrierea / citirea către procesor, nu în mișcare! Tᴀᴋᴎᴍ ᴏϬᴩᴀᴈᴏᴍ, coada de scriere a memoriei stochează datele transferate din memorie către procesor, dar nu este scrisă de procesor în memorie!