JTAG (pronunțat „Jay-tag-ul“ ;. engleză abreviere comună de testare Grupul de Acțiune) - numele grupului de lucru privind dezvoltarea standardului IEEE 1149. Mai târziu, acest declin a fost ferm asociat cu ei dezvoltat interfață hardware specializate bazate pe standardul IEEE 1149.1. Numele oficial al standardului este Standard Access Access Port și Boundary-Scan Architecture. Interfața este concepută pentru a conecta circuite digitale complexe sau dispozitive PCB la echipamente standard de testare și depanare.

În prezent, interfața a devenit un standard industrial. Practic, toate tipurile de circuite integrate digitale complicate sunt echipate cu această interfață pentru:

· Controlul ieșirii microcircuitelor în timpul producției;

· Testarea circuitelor asamblate;

· Chips-uri de firmware cu memorie;

• Debug operațiuni atunci când proiectarea de hardware și software.

Metoda de testare implementată în standard a fost numită Scanare frontală. Numele reflectă ideea inițială a procesului: în microcircuit se alocă blocuri funcționale, ale căror intrări pot fi detașate de restul circuitului, dau combinațiile de semnale specificate și evaluează starea ieșirilor blocului. Întregul proces a fost realizat exclusiv prin comenzi speciale pe interfața JTAG, fără intervenție fizică. De asemenea, a fost dezvoltat un limbaj standard pentru gestionarea acestui proces - Limba de descriere a limitei scanării limită (BSDL).

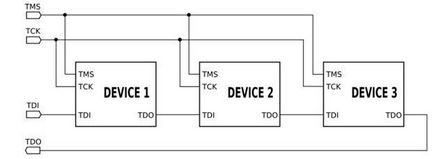

Standardul oferă posibilitatea de a conecta un număr mare de dispozitive (chips-uri) printr-un singur port fizic (conector).

Portul de testare (TAP) este de patru sau cinci pini dedicați ai cipului: TSC, TMS, TDI, TDO și (opțional) TRST.

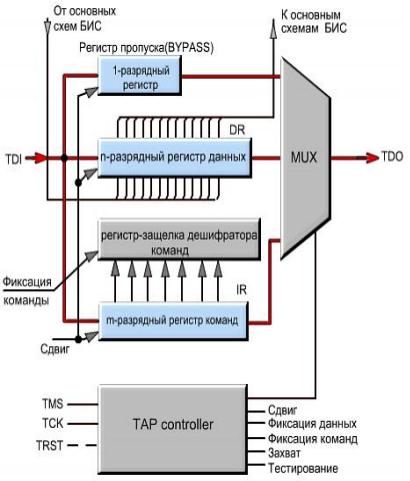

Portul JTAG al unui cip și o celulă pentru scanarea periferică.

Obiectivul funcțional al acestor linii:

TDI (introducerea datelor de test) - introducerea datelor seriale ale scanării periferice. Comenzile și datele sunt introduse în chipul de pe acest pin pe marginea în creștere a semnalului TCK;

TDO (ieșirea datelor de ieșire - ieșirea datelor seriale). Comenzile și datele sunt extrase din cipul de pe acest pin pe marginea descendentă a semnalului TCK;

TCK (ceas de testare) - funcționează cu comanda de scanare periferică încorporată. Frecvența maximă de scanare a celulelor periferice depinde de hardware-ul utilizat și în prezent este limitată la 25 ... 40 MHz [sursa nu este specificată 354 zile];

TMS (selectarea modului de testare) - asigură trecerea circuitului în / din modul de testare și comutarea între diferite moduri de testare.

Funcționarea interfeței JTAG furnizează semnale unității de control integrate în cip. Stările mașinii sunt determinate de semnalele TDI și TMS ale portului de testare. O anumită combinație a semnalelor TMS și TCK oferă intrarea comenzii pentru mașină și execuția acesteia.

Schema de control a interfeței JTAG.

Structura schemei include:

- Trei registre de deplasare (registru de instrucțiuni (IR), registru de by-pass (Bypass) și registru de date (DR);

- Multiplexer de ieșire (MUX);

- Controler (controler TAP).

Fig. 13.1. Interfață hardware JTAG.

Registrul principal este registrul de date, servește ca sursă și receptor al datelor atunci când execută comenzi în JTAG. Din punctul de vedere al dispozitivului de comandă, registrul de date este unul dintre cele trei registre de deplasare incluse între terminale pentru furnizarea de informații de intrare (TDI track) și un terminal de ieșire pentru primirea informațiilor (TDO terminal).

Dacă există mai multe dispozitive care suportă JTAG pe placă, ele pot fi combinate într-un lanț comun. O caracteristică unică a lui JTAG este posibilitatea de a programa nu numai microcontrolerul (sau FPGA), ci și conectarea la pinii chipului de memorie flash. Există două moduri de programare a memoriei flash folosind JTAG: prin bootloader cu schimbul ulterior de date prin memoria procesorului sau prin controlul direct al ieșirilor cipului.

Fig. 13.2. conectați cipuri multiple la o singură interfață.

Software-ul pentru lucrul cu această interfață este implementat de produsele JTAG Live. Familia JTAG Live de produse software este destinată în primul rând dezvoltatorilor care depanază produse noi sau existente. JTAG Live se bazează pe scanarea periferică - o metodă care vă permite să localizați cu exactitate defectele în circuitele digitale. În același timp, produsele JTAG Live nu sunt sisteme automate profesionale; toate testele sunt create manual. Prin urmare, munca nu are nevoie de o listă netă. Pur și simplu selectați ieșirile necesare ale chips-urilor activate JTAG și trageți-le în spațiul de lucru. După aceasta, puteți verifica prezența unui contact între punctele specificate, un scurtcircuit sau puteți lua în considerare o valoare logică pe un anumit circuit. Astfel, este posibil să lucrați chiar și cu ansambluri de bord!

JTAG Live vă permite să utilizați mai multe opțiuni pentru conectarea modulului de testare la un PC. Aceste instrumente funcționează cu programatori USB standard de la Altera și Xilinx. De asemenea, este posibil să conectați controlerul JT3705 / USB de la JTAG Technologies. Puteți începe astăzi absolut gratuit. Descărcați versiunea de bază a JTAG Live și folosiți-o liniștit. Utilizând Buzz, puteți identifica foarte rapid până la două canale de scanare periferică și puteți verifica imediat integritatea lanțului. După verificarea infrastructurii, Buzz vă permite imediat să lucrați cu ieșirile componentelor.

Buzz oferă, de asemenea, o modalitate foarte convenabilă de a verifica prezența unui contact între doi pini, dacă sunt conectați printr-un circuit pe placa de testat. În acest caz, programul emite un sunet familiar tuturor, simulând semnalul unui multimetru obișnuit. În fereastra de măsurare, puteți selecta ieșirea IC, unde ați setat nivelul logic dorit și ați citit nivelul pe orice alt știft al aceluiași sau alt cristal.

Încercați să verificați prezența unei rezistențe de tragere prin instalarea driverului de ieșire corespunzător în cea de-a treia stare (High-Z). Buzz vă permite, de asemenea, să citiți pe un grup de circuite, dacă acestea sunt interconectate, ceea ce depășește capacitățile unui multimetru convențional. Setați o valoare pe piciorul selectat al chipului și verificați acest semnal pe toate celelalte intrări ale dispozitivelor de pe placă.

Dacă doriți să mergeți mai departe decât simple "chimes" și să examinați circuite individuale, puteți lua în considerare utilizarea programelor de creare a testelor JTAG Live Clip și Script. Cu ajutorul lor, puteți salva programe de testare pentru utilizare în producție. Clip este un supliment care vă permite să creați manual testele vectoriale necesare pentru anumite circuite. Script combină bine scanarea periferică și testarea funcțională cu utilizarea limbajului de programare PythonTM încorporat. Cu toate acestea, notăm. că Live Clip și Script sunt programe plătite.

Suport interfață hardware - JT 3705 / USB.

Fig. 13.3. Aspectul controlerului JT 3705 / USB Explorer.

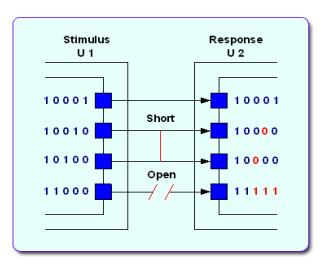

Testarea conexiunii externe cu chip folosind JTAG

• Să presupunem că există două erori în schemă:

• închiderea între liniile 2 și 3 și

• Să presupunem că dispozitivul de închidere apare ca și prin cablu și pauza ca

prezența constantă a logicii 1.

Ris.13.4. Testarea conexiunilor.

O revizuire a instrumentelor JTAG.

ldoolitt / jtag.html), prima încercare de a dezvolta un strat de software pentru a avea acces la gazdă (pentru acces gazdă-side) la porturile JTAG Test de acces. Majoritatea dezvoltatorilor dezvoltă soluțiile lor se suprapun, singularități atunci când încearcă să realizeze portabilitatea între adaptoare JTAG punerea în aplicare a debugger, sau punerea în aplicare a dispozitivelor autodetecția în lanțul JTAG. Încercarea de a dezvolta o comunitate unificată de componente pentru a îndeplini aceste sarcini pe baza unui API comune pentru accesul de nivel mediu la dispozitivele JTAG. Acest lucru permite dezvoltatorilor de aplicații la nivel înalt să nu reinventeze roata prin lucrul cu detalii de nivel scăzut, cum ar fi știfturile JTAG etc.