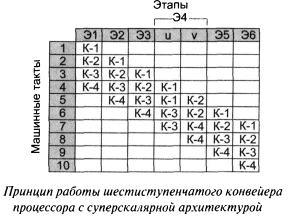

Un procesor construit pe o arhitectură superscalar are 2 (sau mai multe) conducte pentru a executa comenzi. Aceasta vă permite să executați simultan 2 (sau mai multe) comenzi. Pentru a înțelege mai bine fezabilitatea utilizării unei arhitecturi superscaliare în procesor, să aruncăm o privire la exemplul precedent de procesare a conductelor, în care am presupus pentru simplitate că etapa de execuție a comenzii (E4) durează doar un ceas de mașină. Și ce se întâmplă dacă executarea comenzii E4 durează 2 cicluri de mașină? Apoi conducta va eșua, după cum se arată în figură.

Procesorul nu va putea trece la faza de executare a E4 a comenzii K2 până când nu finalizează complet faza de execuție a comenzii K1. Ca rezultat, ciclul de execuție al comenzii K-2 va crește cu 1 ceas de mașină, i. E. în timp ce așteaptă eliberarea conductei în etapa E4. Pe măsură ce comenzile suplimentare ajung pe conducte, unii dintre pașii săi vor funcționa în regim de așteptare (în figură sunt evidențiate în gri).

Pentru a combate nefuncționarea echipamentelor, sunt utilizate mai multe transportoare. În procesorul Intel Pentium au fost utilizate 2 conducte. A devenit primul procesor de familie IA-32 construit pe o arhitectură superscalară. În procesorul Pentium, pentru prima dată au fost utilizate 3 conducte.

Continuăm să considerăm exemplul nostru de transportor cu șase trepte și să introducem în el un transportor (adică al doilea). Ca și înainte, vom presupune că faza de execuție a comenzii E4 durează două cicluri de mașină. Așa cum este arătat în figură, comanda numerotată impare merge la u-pipeline, iar comanda cu un număr par va duce la conducta v. Această abordare vă permite să eliminați timpii de nefuncționare în conductă.

În MP cu o astfel de arhitectură, se utilizează executarea paralelă a comenzilor între mai multe conducte și decizia de executare paralelă a comenzilor este acceptată de echipamentul procesorului în stadiul de execuție. Utilizarea eficientă a unei astfel de arhitecturi necesită o optimizare specială a codului mașinii în compilator pentru a genera perechi de comenzi independente (atunci când rezultatul unei comenzi nu este un argument al celuilalt).

Membrii Superscalar pot emite un număr variabil de instrucțiuni pentru execuție în fiecare bara, iar operarea conductelor lor poate fi planificată static folosind un compilator sau cu ajutorul unui hardware dinamic de optimizare. Mașinile superscalare utilizează paralelism la nivel de comandă prin trimiterea mai multor comenzi dintr-un flux normal de comandă către mai multe dispozitive funcționale.

Într-o mașină tipică superscalară, echipamentul poate distribui 1 până la 8 instrucțiuni într-un singur ciclu de ceas. De obicei, aceste comenzi trebuie să fie independente și să îndeplinească anumite restricții, de exemplu, astfel încât în fiecare ciclu de ceas nu pot fi emise mai multe instrucțiuni de acces la memorie. Dacă orice comandă din fluxul de comandă este dependentă logic sau nu îndeplinește criteriile de emitere, numai comenzile care preced acest lucru vor fi emise pentru execuție. Prin urmare, viteza de emitere a comenzilor în mașinile superscalare este o variabilă

ArhitekturyCisc

Risc arhitectura

MCS-51 (Intel 8051) este o arhitectură clasică de microcontrolere. Pentru aceasta, există un asamblor încrucișat ASM51, lansat de MetaLink.

În plus, multe companii de software, cum ar fi IAR sau Keil, au introdus versiuni proprii de asamblare. Într-o serie de cazuri, utilizarea acestor asamblori este mai eficientă datorită unui set convenabil de directive și a prezenței unui mediu de programare care combină un asamblator profesionist și limbajul de programare C, un program de depanare și un manager de proiect.

În prezent există 2 compilatoare Atmel (AVRStudio 3 și AVRStudio4). Cea de-a doua versiune este o încercare de a stabili un prim nu foarte reușit.

În cadrul proiectului AVR-GCC (de asemenea, WinAVR), există un compilator avr-as (este portat pentru asamblorul AVR GNU ca și de la GCC).

De asemenea, există un compilator minimalist avra [1].