frecvență dinamică schimbare de fază PLL

Site-ul nostru a fost deja o serie de articole despre PLL.

PLL - este, pur și simplu, un built-in ceas FPGA. Acesta permite de la un ceas de intrare pentru a sintetiza alte câteva cu o frecvență predeterminată, ciclu și, dacă se dorește, cu o anumită deplasare de fază inițială.

Acum vreau să vorbesc despre posibilitatea de a se schimbă în mod dinamic faza a PLL de ceas. Această caracteristică este în PLL de FPGA. ca Cyclone III, Cyclone IV, în MAX10 și altele. Pentru a-ți spun adevărul, eu însumi, și asta e doar faptul că am citit cu această funcție în PLL. Chiar înainte de a face acest lucru, nu era nevoie, iar acum există un proiect, în cazul în care acesta poate fi necesar. PLL schimbare de fază - se pare ca singura modalitate de a controla cu precizie întârzieri de semnal.

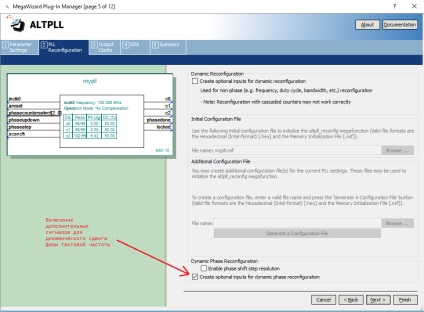

Deci, într-un expert există un număr de file 2: PLL Reconfigurarea. acolo a pus o verificare: Crearea intrări opționale pentru reconfigurare fază dinamică.

De îndată ce am pus o verificare la stânga arată expertul PLL bloc și există noi intrări și ieșiri, care nu existau înainte.

Prin intermediul acestor semnale pot fi controlate faze orice PLL ceas de ieșire.

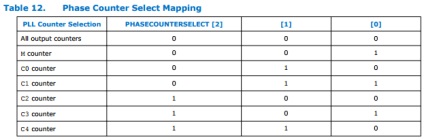

semnal phasecounterselect [2..0] pentru a selecta care dintre contoarele interne PLL se va schimba. Documentația de pe PLL FPGA MAX10 există un astfel de tabel:

Astfel, în cazul în care este necesar să se schimbe faza de ceas de ieșire c0, apoi necesitatea de a pune phasecounterselect = 3'b010. În cazul în care defazaj frecvența de ceas de c1, apoi phasecounterselect = 3'b011.

Schimbarea de fază a semnalului de ceas de ieșire este inițiată prin setarea phasestep o unitate logică. Acesta este începutul defazajului de tranzacție. Pentru o singură fază „tranzacție“ a frecvenței selectate este deplasată cu o fază a unei etape (mai mult pe aceasta mai târziu). La sfârșitul fazei de ceas schimbare PLL semnal prezintă phasedone. Dacă se dorește defazaj chiar, este necesar să se reducă mai întâi phasestep o logică zero, iar apoi din nou setat la una, deoarece tranzacția următoare.

semnalul phaseupdown determină direcția de deplasare de fază, înainte sau înapoi.

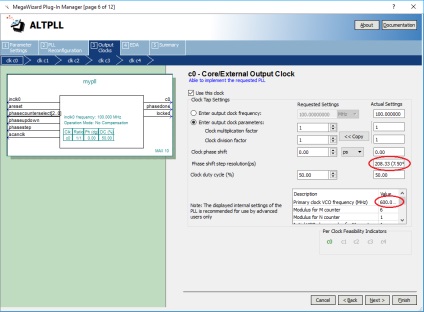

Acum, întrebarea principală: cât de mult putem schimba de fapt, faza de ceas? Documentația prevede în mod clar că trecerea de faza pas - o perioadă de 1/8 din frecvența VCO PLL. VCO - oscilator intern de tensiune controlat. Din păcate, expertul PLL nu este posibil să se prezinte în mod clar frecvența Fvco dorită. Se poate vedea numai ceea ce se întâmplă cu setările noastre.

De exemplu, în cazul în care frecvența de intrare la 100MHz Reglaj frecvență de ieșire și PLL am pus 100MHz, expertul însuși spune că Fvco în interiorul PLL este 600MHz.

Aceasta înseamnă că faza de rezoluție, ceas de o fază de compensare poate fi de aproximativ 7,5 grade, este posibil să se deplaseze frecvența față de 208,33 picosecunde. Este posibil să crească rezoluția?

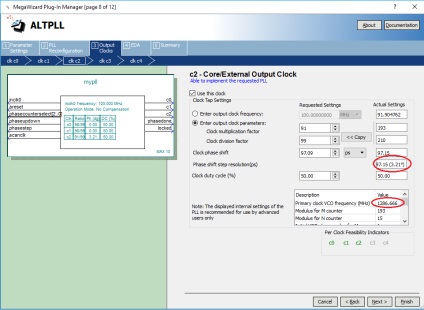

Am reușit să iau aici sunt factorii:

- randament PLL c0, multiplicator 98, diviziunea coeficient 99, frecvența rezultantă

În același timp, am vedea că Fvco = 1286,666MGts și faza de rezoluție a fost 97,15 ps. Aceasta este o fază foarte înaltă rezoluție.

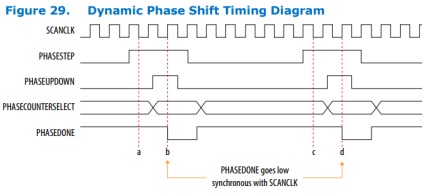

Documentația privind PLL există o astfel de diagramă de timp care arată modul în care pentru a produce o schimbare de fază dinamică:

Vă sugerez să încercați acest caz în ModelSim prosimulirovat.

Fac un proiect simplu în Intel Cvart Prime Lite, în cazul în care nu există aproape nimic altceva decât un PLL și o logică simplă, care schimbă periodic faza c1 frecvența de ieșire. Modul de nivel superior a proiectului am scris pe Verilog:

top modul (

intrare KEY0 sârmă,

intrare key1 sârmă,

intrare CLK100MHZ sârmă,

sârmă inout [19: 0] IO,

sârmă de ieșire [7: 0] LED

);

wc0 sârmă;

WC1 sârmă;

wc2 sârmă;

sârmă wlocked;

wpdone sârmă;

reg phase_step = 1'b0;

mypll_ mypll (

.areset (1'b0),

.inclk0 (CLK100MHZ),

.phasecounterselect (3'b011),

.phasestep (phase_step),

.phaseupdown (1'b1),

.scanclk (wc0),

.c0 (wc0),

.c1 (WC1),

.c2 (wc2),

.blocat (wlocked),

.phasedone (wpdone)

);

reg [3: 0] cnt = 0;

întotdeauna @ (posedge wc0)

cnt <= cnt + 1;

întotdeauna @ (negedge wc0)

if (cnt == 4'hF)

phase_step <= 1'b1;

altfel

if (wpdone == 1'b0)

phase_step <= 1'b0;

aloca LED = 0;

atribui IO [0] = wc0;

atribui IO [1] = WC1;

atribui IO [19: 2] = 0;

Fac un proiect ca și carte de Marsohod3bis cip FPGA MAX10. Deci, am aici are semnale de intrare KEY0 și key1, care nu este folosit, ci să fie. Semnalele de ieșire cu LED-uri nu sunt folosite, dar ieșirile IO [0] și IO [1] Am adus c0 ieșirile și c1 din PLL. Acest lucru este de a face convenabil pentru a observa în simulator.

Aici, în toate procesele de proiect au loc la o frecvență c0, iar aceeași rată se aplică scanclk. Decăderea aceeași frecvență setat și resetat phase_step.

Testbench de simulare nu face nimic special, bine, care este furnizează numai modulul de test este original frecvența de ceas de 100MHz.

`1ns Grafic de timp / 10ps

// presupunem ceas de bază este 100Mhz

reg clk;

clk inițială = 0;

mereu

# 5 clk =

sârmă [7: 0] w_led;

sârmă [19: 0] w_io;

top top_inst (

.CLK100MHZ (clk),

.KEY0 (1'b1),

.Key1 (1'b1),

.IO (w_io),

.LED-ul (w_led)

);

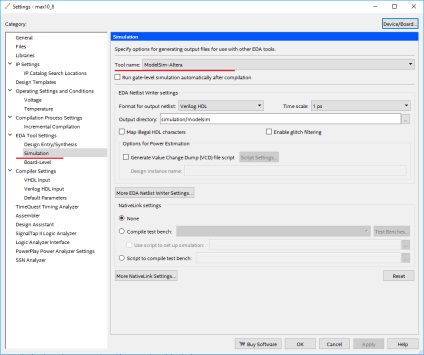

Pentru că vreau să văd un ceas destul de mici faze offset, atunci ar fi, desigur, a vrut să organizeze o simulare de proiect temporar în ModelSim. Pentru aceasta, am in setarile proiectului pe care le voi folosi pentru simulare ModelSim-Altera. În același timp, mă aștept să văd proiectele fișiere de ieșire SDO sau SDF-tip generate.

Din păcate, kvartus mea opinie diferită.

Când compilați proiectul, acesta afișează mesajul: Avertizare (10905): a generat netlist de simulare funcțională EDA, deoarece este tipul netlist numai acceptat pentru acest dispozitiv. Se pare că pentru chips-uri MAX10 în timp ce se poate face numai de simulare funcțională? Kvartus generat doar mine fișier top.vo

Ceea ce văd graficele de sincronizare: Modul periodic de sus expune semnal phase_step și PLL puls scurt corespunde semnalului phasedone zero.

Dacă nu măriți și să încerce să ia în considerare mai multe frecvențe de ceas fază, devine imediat evident că faza semnalului IO [1], pe care l-am conectat la ieșire PLL c1 se mișcă înainte, imediat după semnalul phasedone:

Se pare că, în simulare pot vedea modul în care se schimbă faza a ceasului. Apropo, notați cât de mică pas fază în comparație cu perioada de frecvență în sine. efect de schimbare de fază poate încerca, de asemenea, să folosească circuitele de măsurare a sinalov întârziere în reflectometre și alte dispozitive de măsurare.

Voi încerca să facă proiectul unui instrument de măsurare simplu, care poate evalua întârzierea de propagare a semnalului, cu o precizie de aproximativ 100 picosecunde.

Dacă megavizarde tick „permite faza de rezoluție pas schimbare“, este mai ușor de a controla frecvența VCO. Frecvența de ieșire poate fi specificată rotund - 100 MHz și rezoluție pas de schimbare de fază „- 96ps pentru 1300MGts VCO, 104ps pentru 1200MGts VCO, și așa că nu trebuie să toeing fărâme ..

Puteți adăuga testbench la proiect și setați NativeLink setarea „Compile banc de probă“. Apoi, simularea va lucra într-un singur clic (Tools -> instrument de simulare -> Run RTL Siumulation) „din cutie“, nu va trebui să creeze proiecte și să adăugați biblioteci în ModelSim, acesta va funcționa

„Voi încerca să facă proiectul unui instrument de măsurare simplu, care poate evalua întârzierea de propagare a semnalului, cu o precizie de aproximativ 100 de picosecunde“ - așteaptă cu nerăbdare să!

10Gvyb / s, dar mâinile nu au ajuns.