Circuitul matrice ililogicheskaya matrice este o grilă de linii ortogonale, intersecțiile din care elemente semiconductoare pot fi montate: diode sau tranzistori care implementează circuitele necesare.

Pentru a permite programarea matricei, aceste diode sau tranzistori conectat la conductori din matricea corespunzătoare prin intermediul web fuzibil. În timpul programării, aceste jumperii sau ars, sau la stânga, în funcție de schema, care ar trebui să fie puse în aplicare prin intermediul unei matrice. Implementarea circuitului matrice orientat de funcții booleene de scară largă integrate noduri circuite (LSI).

Astfel, din cauza structurii sale matrice obținută prin programarea dispozitivului Raman dorit. Prin urmare, o astfel de structură nazyvayutprogrammiruemye matrice logică (PLA).

PLA, în general, au un design de circuit cu două niveluri. prima dintre care sunt cerute de conjuncția, iar al doilea - disjuncție. Ambele matrici sunt conectate în cascadă.

Există, de asemenea, PLA, având în componența sa de elemente de memorie internă. O astfel de PLA caracterizat registru de memorie cifre.

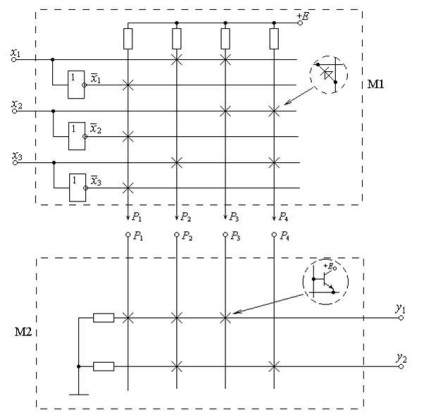

Să considerăm matricea din Fig. 17.1.

matrice M1 are trei posibile x1 de intrare. x2, x3, șase orizontale și patru bare verticale. autobuz x1 orizontală. x2, x3 în M1 sunt de intrare și P1 ... P4 verticală - ieșire.

P ieșiri sunt numite linii de termen.

Intrare x1 autobuz. x2, x3 sunt conectate la autobuze verticale, atât direct, cât și prin invertoare (anvelopa ..).

MatritsaM1rabotaet kakdeshifrator. ieșirile de care sunt termeni conjunctive P1 ... P4. O metodă de elemente de comutare semiconductoare (de exemplu, diode) la intersecții, marcate prin cruci, permite realizarea pe oricare dintre ieșirile, orice combinație a variabilelor de intrare, adică Funcția I.

Într-adevăr, atunci când unitatea apare pe una dintre intrări xi. ieșirea invertorului corespunzătoare este zero logic. Dacă, de exemplu, există un jumper pe linia xi orizontală. unic xi potențială linie se închide „a“ dioda și un termen care corespunde liniei verticale este o tensiune de aproximativ egală cu tensiunea (+ E), adică unitatea.

Dacă jumper este în linie de intrare inversă, nivelul scăzut al liniei deschide „a“ dioda și aproape întregul curent va curge prin linia de magistrală verticală a unui autobuz orizontal, vertical lăsând fără alimentare, adică de ieșire este un zero logic.

Figura 17.1 - Programmable Array Logic:

M1 - conjuncție cu matrice; M2 - matricea disjuncție

Menținerea unui nivel ridicat de unități logice pe anvelopă verticală PN este posibilă numai atunci când toate diode pe linie va fi închisă, ceea ce este posibil numai atunci când nivelurile de unități logice de pe toate liniile orizontale, care sunt conectate la PN de autobuz pe verticală.

Astfel, o linie verticală este pusă în aplicare variabile conjunction PN. conjuncțiile conjunctions M1 Matrix realizează funcții conform ecuației logica:

matrice M2 are patru verticale autobuz P1 ... P4 și două y1 orizontale și y2. Metoda de tranzistori la intersecții ale anvelopei permite implementarea oricare dintre ieșirile sale orice disjuncție (OR funcții) ale variabilelor de intrare. In matricea de intrare M2 este magistrala verticală și ieșire - orizontală.

În această matrice prezintă un exemplu de implementare disjuncțiilor descrise de expresii matematice

Disjuncțiilor matrice tranzistorului M2 la desemnat intersecția ortogonală cruce de linii vor fi deschise numai în cazul în care curentul în linia verticală, iar în absența curentului - închis. Pentru matricea M2 suficient pentru cel puțin un tranzistor a fost deschis pe linia orizontală. apoi YJ de ieșire este un nivel logic. Numai absența curentului în toate liniile orizontale oferă un zero logic pe magistrala verticala. care definește funcționarea disjuncție. În acest exemplu (fig. 17.1) este realizat prin funcția descrisă de ecuațiile (17.2).

Dacă vom combina cele două matricele M1 și M2, așa cum se arată în Fig. 17.2, circuitul rezultat va implementa un sistem de funcții booleene

Construcție de circuite cu o structură de matrice reduce la determinarea punctelor de intersecție ale anvelopei în cazul în care dispozitivele semiconductoare urmează să fie incluse. Tabel. 17.1 coloane conțin x1 variabilă. XL funcții și U1. Yn.

Realizarea funcțiilor sistemului matricele M1 și M2 pot fi afișate sub formă de tabel. 17.1.

La rândul Reprimarea j-și coloana XL (l =) sunt scrise:

- 1 dacă xi variabila intră jth conjuncție fără inversiune;

- 0 dacă xi variabila intra jth inversiune c conjuncție;

- cratimele (-), în cazul în care variabila x i la j-lea nevhodit conjuncție.

La Suprimarea j th rând și o coloană sunt scrise:

- 1 dacă partea j-conjugării yn disjuncție;

- punctul (# 8729;) în cazul în care j-lea nu este în conjuncție yn disjuncție.

Prin urmare, orice sistem de funcții booleene y1. Yn variabilelor de intrare x1. XL poate fi implementat într-un circuit de matrice cu două nivele, la primul nivel, care sunt diferite conjuncții P1. PB. în timp ce al doilea - un U1 disjuncție. Yn conjuncții corespunzătoare. Ca urmare a construcției de circuite cu o structură de matrice se reduce la determinarea punctelor de intersecție ale pneului, în cazul în care urmează să fie incluse diode sau tranzistori.

Complexitatea realizării matricei estimată capacitatea totală (aria) a matricelor. În general, într-un circuit cu intrări L; N ieșiri și verticalele zona este

Acesta poate fi un simplu destul de principii pentru a construi un dispozitiv digital combinațional bazat pe PLA.

Etapa principală a dezvoltării este de a face masa de programare PLA, care este procedurile de instruire epuizare poduri inutile în matrice.

Pentru a extinde posibilitățile funcționale ale utilizării disponibile în comerț PLA versiunea simplificată, de exemplu, supape programabile matrice, matrice logica programabilă, o multiplexoare programabile etc.